Device family support, Device family support –2 – Altera Interlaken MegaCore Function User Manual

Page 8

1–2

Chapter 1: About This MegaCore Function

Device Family Support

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

■

Supports fast simulation by allowing configuration without high-speed

transceivers

■

Supports up to 127.5 Gbps raw bandwidth

■

Supports dynamically configurable BurstMax and BurstShort values

■

Provides Avalon-ST interfaces on the transmit and receive datapaths

■

Supports two logical channels in out-of-the-box configuration

■

Supports optional user-controlled in-band flow control with 1, 8, or 16 16-bit

calendar pages

■

Supports optional out-of-band flow control blocks for lane status, link status, and

one calendar page

lists the theoretical raw bandwidth of the Interlaken MegaCore function in

the supported combinations of lane rate and number of lanes.

Device Family Support

defines the device support levels for Altera IP cores.

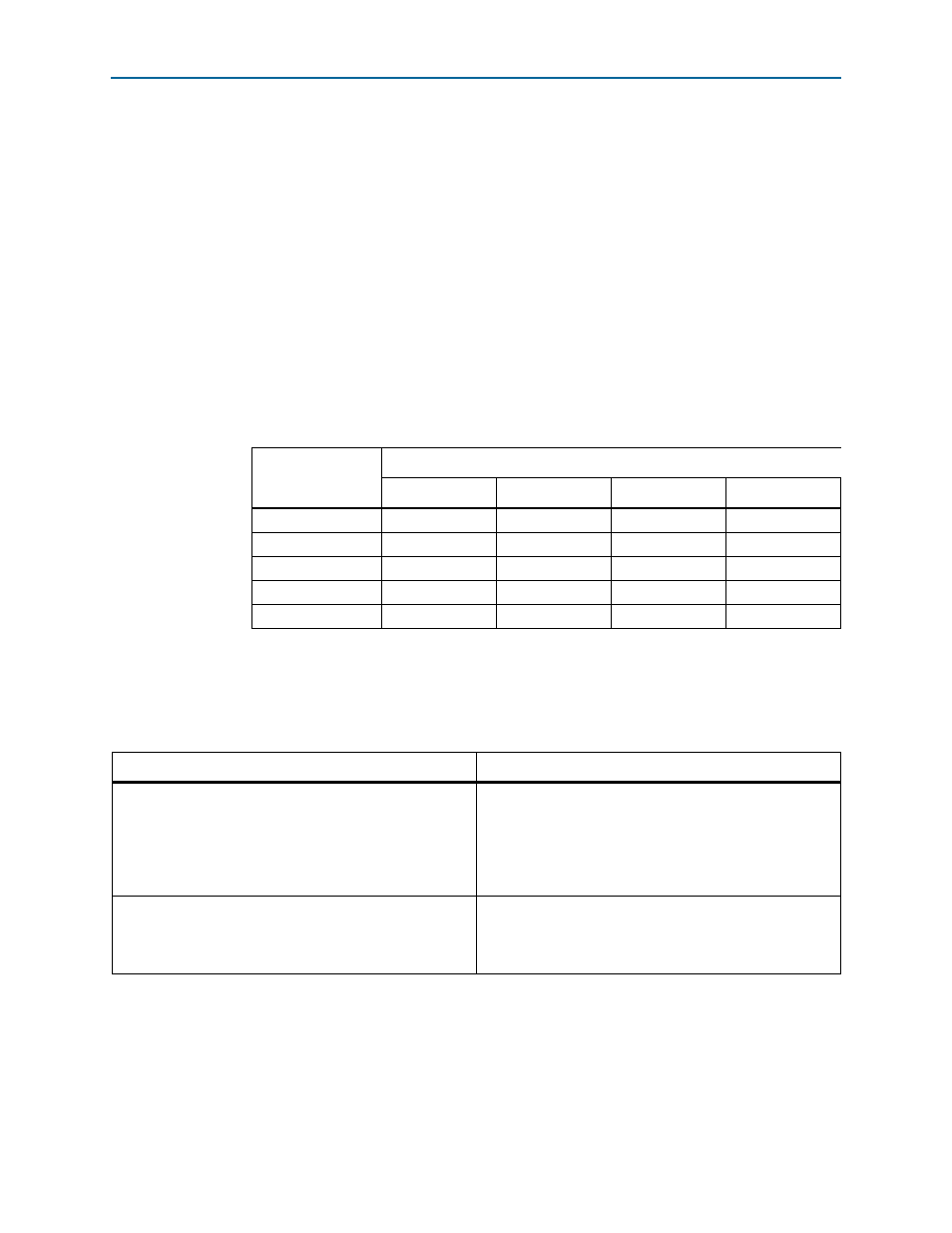

Table 1–1. Theoretical Raw Aggregate Bandwidth in Gbps

Number of Lanes

Lane Rate (Gbps)

3.125

6.25

6.375

10.3125

4

12.50

25.00

25.50

—

8

25.00

50.00

51.00

—

10

—

62.50

63.75

—

12

—

75.00

76.50

123.75

20

—

125.00

127.50

—

Table 1–2. Altera IP Core Device Support Levels

FPGA Device Families

HardCopy Device Families

Preliminary support—The core is verified with preliminary

timing models for this device family. The IP core meets all

functional requirements, but might still be undergoing timing

analysis for the device family. It can be used in production

designs with caution.

HardCopy Companion—The IP core is verified with

preliminary timing models for the HardCopy companion

device. The IP core meets all functional requirements, but

might still be undergoing timing analysis for the HardCopy

device family. It can be used in production designs with

caution.

Final support—The IP core is verified with final timing

models for this device family. The IP core meets all

functional and timing requirements for the device family and

can be used in production designs.

HardCopy Compilation—The IP core is verified with final

timing models for the HardCopy device family. The IP core

meets all functional and timing requirements for the device

family and can be used in production designs.