Altera Interlaken MegaCore Function User Manual

Page 78

B–6

Appendix B: Excluding Transceivers for Faster Simulation

Reset in Interlaken MegaCore Functions Without Transceivers

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

Reset in Interlaken MegaCore Functions Without Transceivers

If you turn on Exclude transceivers, your Interlaken MegaCore function does not

include a reset controller block. Therefore, you must implement the required reset

sequence yourself. This section lists the individual reset signals available in these

variations and describes the reset sequence your testbench must enforce.

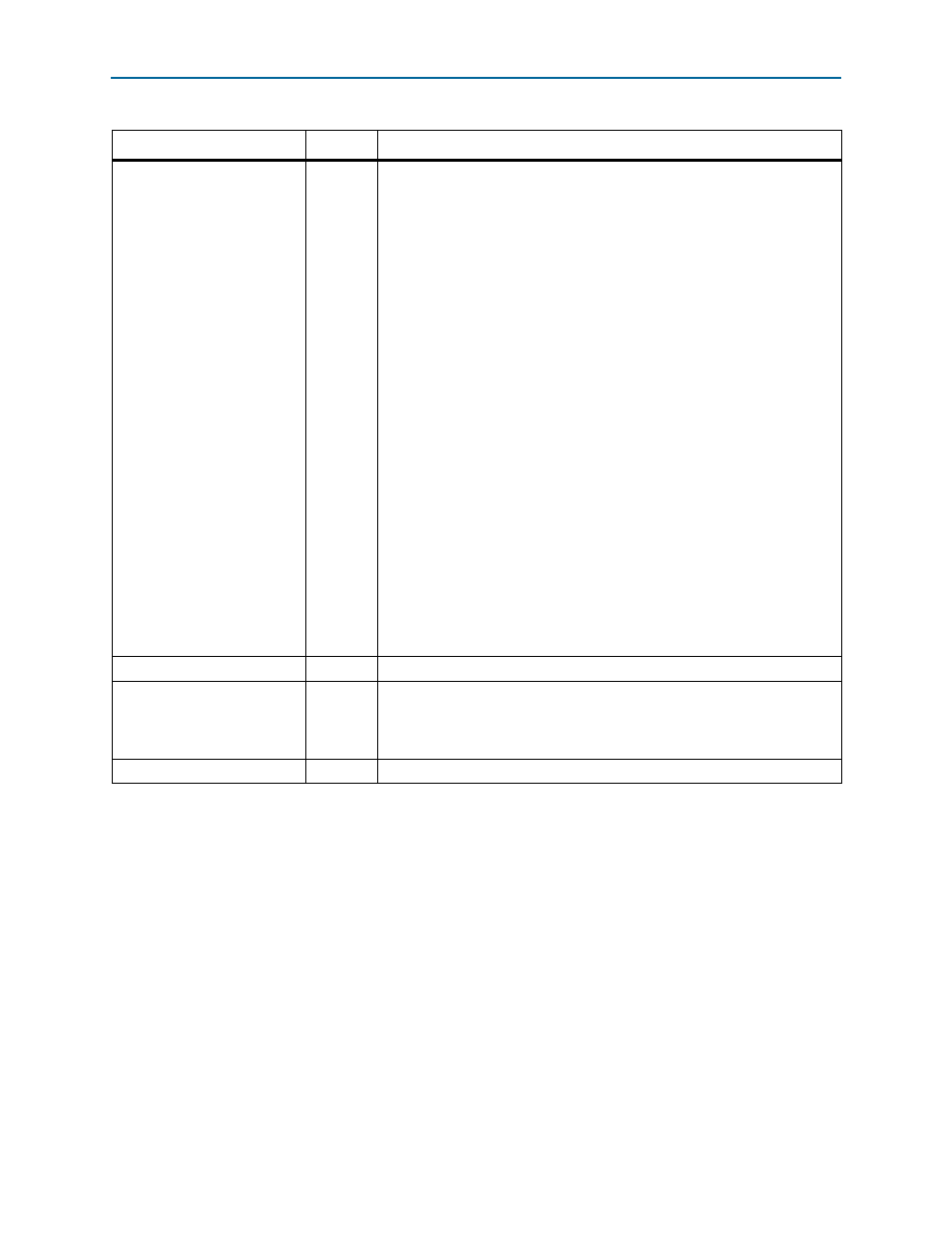

rx_dataN_export[S:0]

Input

Parallel receive data interface. N = 0 for 4-lane variations; N = {0,1} for 8- and

10-lane variations, N = {0,1,2} for 12-lane variations, and N = {0,1,2,3} for

20-lane variations.

The width of the port for each value of N is the transceiver datapath width

times the number of channels used on an Altera device transceiver in

variations that include the transceivers. For the 12-lane, 10-Gbps variation,

the transceiver datapath width is 40. For all the other variations, the

transceiver datapath width is 20. The number of channels is 4 for 4-, 8-, and

12-lane variations, and 5 for 10- and 20-lane variations. (S = calculated port

width – 1).

Lane 0 holds the MSB of the input data, which is input to rx_dataN_export

with the highest value of N. Refer to

through

, ignoring the transceivers in the figures.

In an 8-lane variation, rx_data1_export[79:60] connects to lane 0,

rx_data1_export[59:40]

connects to lane 1, and so on;

rx_data0_export[59:40]

connects to lane 5,

rx_data0_export[39:20]

connects to lane 6, and

rx_data0_export[19:0]

connects to lane 7.

In a 20-lane variation, rx_data3_export[99:80] connects to lane 0,

rx_data3_export[79:60]

connects to lane 1, and so on;

rx_data2_export[99:80]

connects to lane 5,

rx_data2_export[79:60]

connects to lane 6, and so on;

rx_data1_export[99:80]

connects to lane 10;

rx_data1_export[19:0]

connects to lane 14;

rx_data0_export[99:80]

connects to lane 15, and

rx_data0_export[19:0]

connects to lane 19.

tx_lane_c_clk

Input

Clocks the Interlaken transmit lanes.

rx_lane_clkN_export[M:0]

Input

Clock inputs from external transceivers. N = 0 for 4-lane variations; N = {0,1}

for 8- and 10-lane variations, N = {0,1,2} for 12-lane variations, and N =

{0,1,2,3} for 20-lane variations. The width of the port is 4 (M=3) for 4-, 8-, and

12-lane variations, and 5 (M=4) for 10- and 20-lane variations.

common_rx_c_clk

Output

This signal is tied to 0 when the external transceiver interface is exposed.

Table B–1. External Transceiver Interface Signals (Part 2 of 2)

Signal

Direction

Description