Specifying constraints, Hard pll assignment constraints, Specifying constraints –7 – Altera Interlaken MegaCore Function User Manual

Page 19: Hard pll assignment constraints –7

Chapter 2: Getting Started

2–7

Specifying Constraints

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

Specifying Constraints

Altera provides a Synopsys Design Constraints (.sdc) file that you must apply to

ensure that the Interlaken MegaCore function meets design timing requirements. The

script automatically constrains the system clocks and the reference clock based on the

data rate you specify. If your design includes multiple instances of the Interlaken

MegaCore function, you must edit the .sdc file to ensure that each instance name

appears correctly in the file.

The Quartus II software v12.0 requires that you add the following additional

constraints manually:

■

Hard PLL Assignment Constraints

■

The following sections describe the constraints you must add manually.

Hard PLL Assignment Constraints

The .sdc script provided with the Quartus II software v12.0 requires that you add

hard PLL assignment constraints to the Quartus Settings File (.qsf) before you

compile your design. You can add these constraints directly to the .qsf, or you can use

the Quartus II Assignment Editor.

You must add the following hard transceiver PLL assignments before compilation:

set_location_assignment IOBANK_<quad_location> -to <PLL_path>

where

■

<quad_location>

is any valid quad location on your device. It may be any of QLn

or QRn, for n in {0,1,2,3}, depending on the device

■

<PLL_path>

is "*|lt_ntrlkn_hsio_bank_*:alt_ilk_hsio_bank_<n>|*|tx_pll*0"

for any valid high-speed I/O (HSIO) bank number <n>

The valid HSIO bank numbers depend on the number of lanes in your Interlaken

MegaCore function variation.

shows the valid HSIO bank numbers.

To add the constraint using the Assignment Editor, perform the following steps:

1. Open your Quartus II project in the Quartus II software.

2. On the Processing menu, point to Start and click Start Analysis & Elaboration.

The analysis and elaboration process might take several minutes to complete.

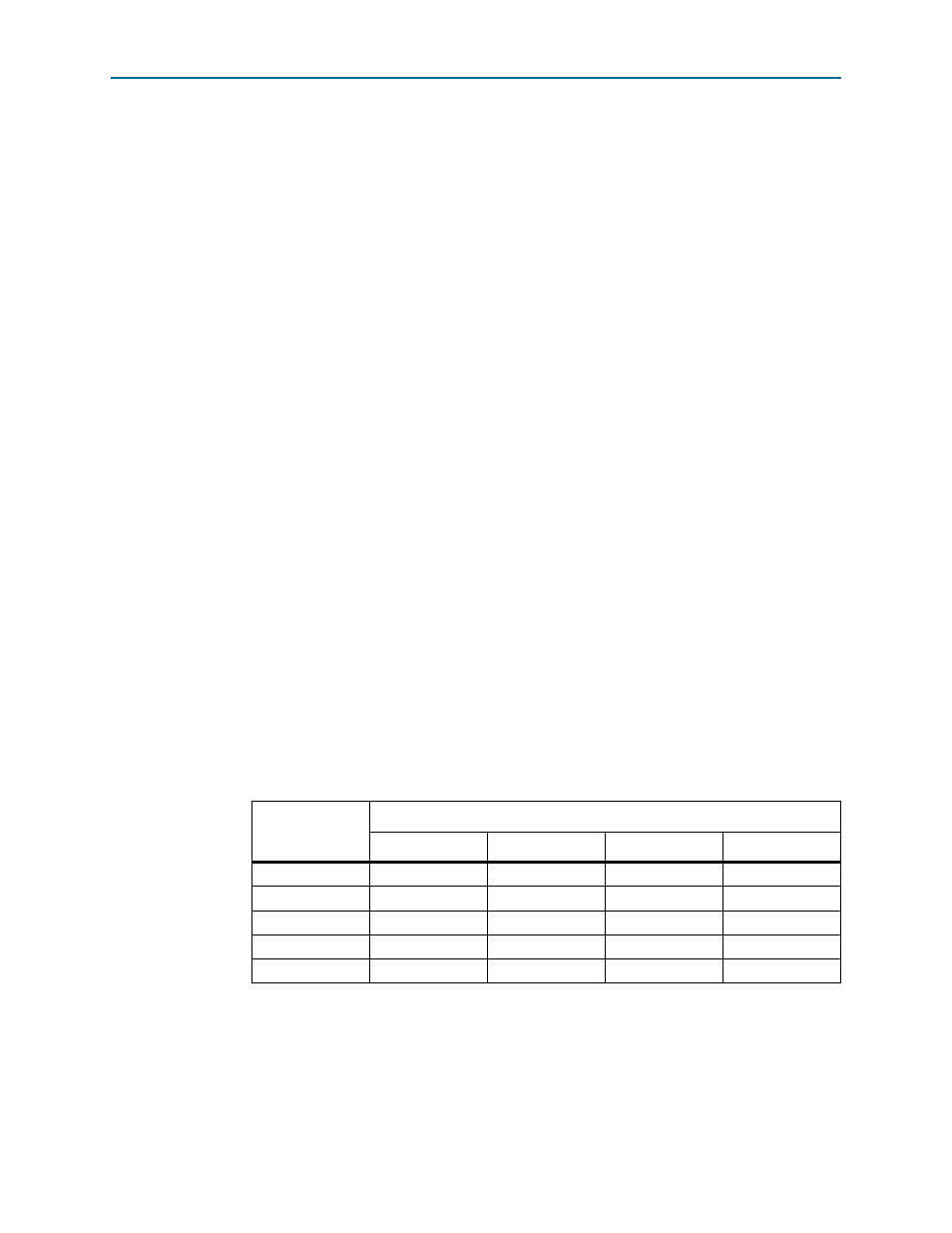

Table 2–1. Valid HSIO Bank Numbers Depending on Number of Lanes

Number of Lanes

Valid HSIO Bank Numbers

0

1

2

3

4

v

—

—

—

8

v

v

—

—

10

v

v

—

—

12

v

v

v

—

20

v

v

v

v