Clocking and reset structure, Megacore function mac clock domains, Interlaken interface clocks – Altera Interlaken MegaCore Function User Manual

Page 31: Clocking and reset structure –5

Chapter 4: Functional Description

4–5

Clocking and Reset Structure

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

Clocking and Reset Structure

The Interlaken MegaCore function has a variable number of clock domains,

depending on whether the MegaCore function includes or excludes transceivers, and

on whether it includes or excludes the out-of-band flow control block.

In addition to the high-speed clock domains inside the device transceivers, some of

which also clock the PCS lanes, the Interlaken MegaCore function contains two MAC

clock domains for the receive and transmit directions, four out-of-band flow control

block clocks, and clocks for the Interlaken interface.

For information about the clocks visible in your Interlaken IP core functional

simulation model if you turn on Exclude transceivers, refer to

Transceivers for Faster Simulation

For recommended clock rates, refer to

“Interlaken MegaCore Function Recommended

.

MegaCore Function MAC Clock Domains

The Interlaken MegaCore function MAC blocks have the following two clock

domains:

■

rx_mac_c_clk

—clocks the RX MAC block.

■

tx_mac_c_clk

—clocks the TX MAC block.

Altera recommends that the same clock drive the rx_mac_c_clk and tx_mac_c_clk

clocks.

Interlaken Interface Clocks

If you turn off Exclude transceiver, your Interlaken MegaCore function has the

Interlaken interface clocks shown in

Table 4–2

.

1

For all Interlaken MegaCore variations except the 8-lane, 3.125-Gbps variation, Altera

recommends that you drive the rx_mac_c_clk and tx_mac_c_clk clocks with the

tx_coreclkout

clock. Refer to

“Interlaken MegaCore Function Recommended Clock

For information about the Interlaken link facing clocks if you turn on Exclude

transceiver

, refer to

Appendix B, Excluding Transceivers for Faster Simulation

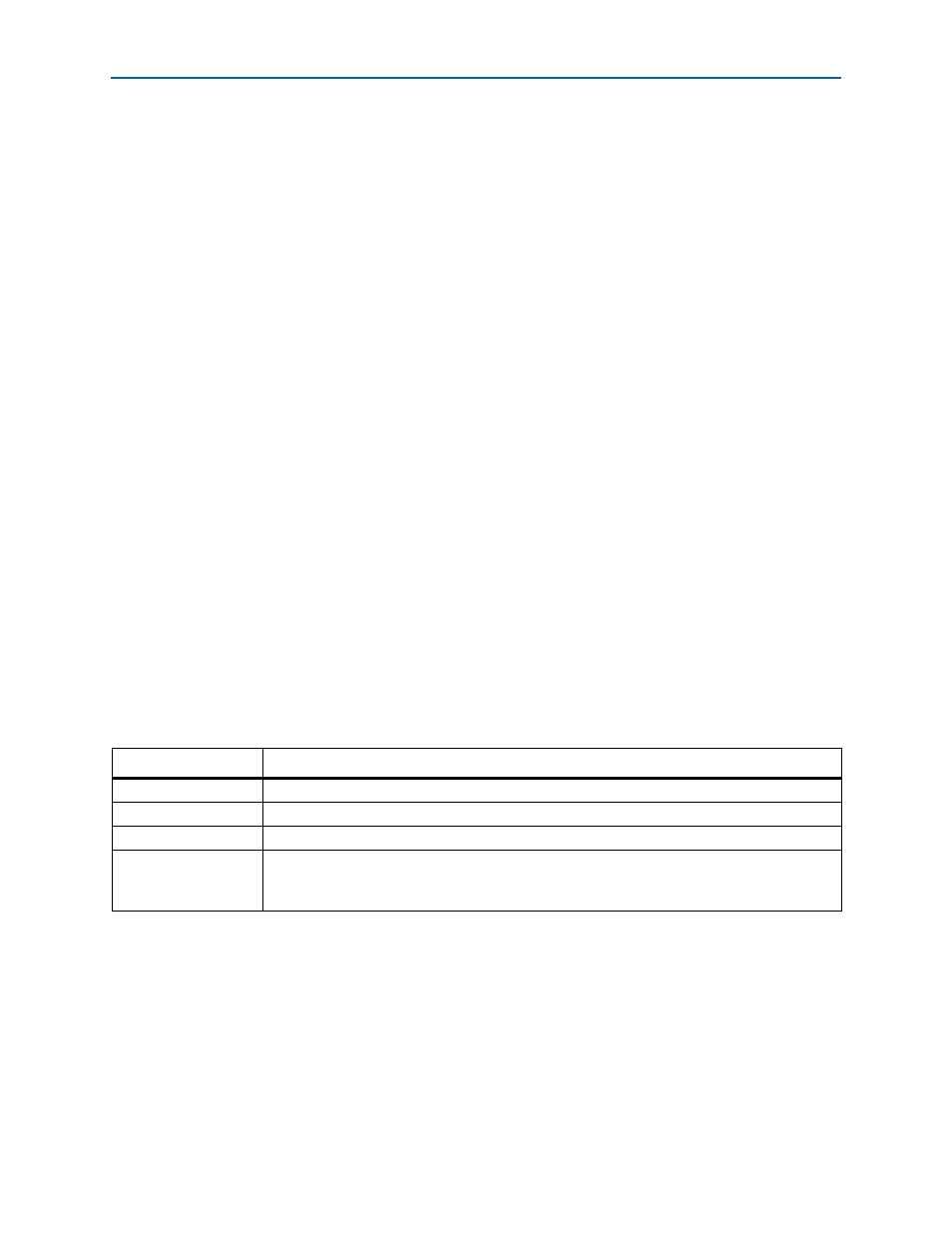

Table 4–2. Interlaken Interface Clocks

Clock Name

Description

ref_clk

Reference clock for the RX and TX transceiver PLLs

cal_blk_clk

Transceiver calibration-block clock

rx_coreclkout

Clocks the RX PCS block. This clock is derived from the physically central RX lane clock.

tx_coreclkout

Clocks the TX PCS block. This clock is derived from the master TX clock from transceiver block 0.

It drives all the transceiver block clk_in clocks, as well as the transmit lanes from the TX PCS

block to the HSIO block.