Mac clock verified frequency, Mac clock verified frequency –9, R to – Altera Interlaken MegaCore Function User Manual

Page 35: Interlaken megacore function recommended, Interlaken megacore function recommended clock, Figure 4–6, Show the

Chapter 4: Functional Description

4–9

Clocking and Reset Structure

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

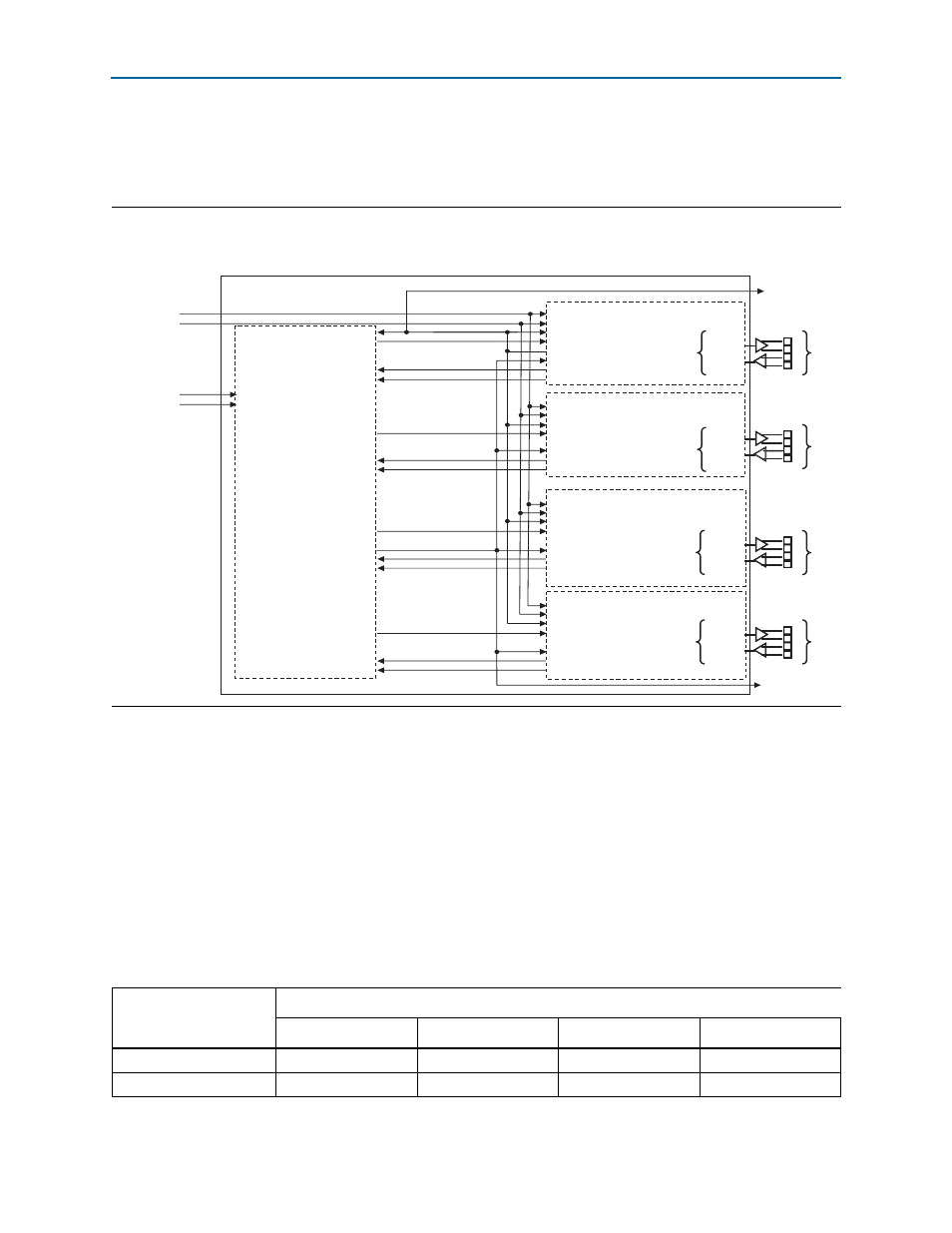

shows the clock diagram for a 20-lane Interlaken MegaCore function. This

variation uses the transceivers in PMA Direct mode. For more information, refer to

“High-Speed I/O Block” on page 4–22

.

Interlaken MegaCore Function Recommended Clock Rates

This section describes the recommended frequencies for the Interlaken MegaCore

function clocks.

MAC Clock Verified Frequency

The Altera Interlaken MegaCore function supports the number of lanes and lane rate

combinations shown in

. The verified MAC clock rates for each

variation depend on the lane rate.

shows the MAC clock frequencies at

which the Interlaken MegaCore function was verified. The MAC clocks are the

tx_mac_c_cl

k and rx_mac_c_clk clocks.

Figure 4–6. Clock Diagram for 20-Lane Interlaken MegaCore Function

cal_blk_clk

ref _clk

clk_in

tx_datain[99:0]

clk_out (master TX clock)

common_rx_clk

rx_dataout[99:0]

rx_clk[4:0]

tx_lane_clk

tx_data[99:0]

rx_data[99:0]

rx_clk[4:0]

tx_data[199:100]

rx_data[199:100]

rx_clk[9:5]

tx_data[299:200]

common_rx_coreclk

rx_data[299:200]

rx_clk[14:10]

tx_data[399:300]

rx_data[399:300]

rx_clk[19:15]

HSIO Bank 0

(in PMA Direct mode)

cal_blk_clk

ref _clk

clk_in

tx_datain[99:0]

common_rx_clk

rx_dataout[99:0]

rx_clk[4:0]

HSIO Bank 1

(in PMA Direct mode)

HSIO Bank 2

(in PMA Direct mode)

HSIO Bank 3

(in PMA Direct mode)

tx_pin[4:0]

rx_pin[4:0]

tx_pin[4:0]

rx_pin[4:0]

cal_blk_clk

ref _clk

clk_in

tx_datain[99:0]

common_rx_clk

rx_dataout[99:0]

rx_clk[3:0]

tx_pin[4:0]

rx_pin[4:0]

cal_blk_clk

ref _clk

clk_in

Lanes 0 to 4

tx_datain[99:0]

common_rx_clk

rx_dataout[99:0]

rx_clk[4:0]

tx_pin[4:0]

rx_pin[4:0]

rx_coreclkout

tx_coreclkout

x5

x5

x5

Lanes 5 to 9

Lanes 10 to 14

Lanes 15 to 19

x5

tx_mac_clk

rx_mac_clk

tx_mac_c_clk

rx_mac_c_clk

cal_blk_clk

ref_clk

TX MAC

and PCS

RX MAC

and PCS

Table 4–3. Verified MAC Block Frequencies in MHz (Part 1 of 2)

Number of Lanes

Lane Rate (Gbps)

3.125

6.25

6.375

10.3125

4

156.25

312.50

318.75

—

8

200.00

312.50

318.75

—