Interlaken interface data and clock signals, Interlaken interface data and clock signals –2, Table 5–1 – Altera Interlaken MegaCore Function User Manual

Page 54

5–2

Chapter 5: Signals

Interlaken Interface and External Transceiver Interface Signals

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

Interlaken Interface Data and Clock Signals

lists the Interlaken interface data and clock signals when you turn off

Exclude transceivers

.

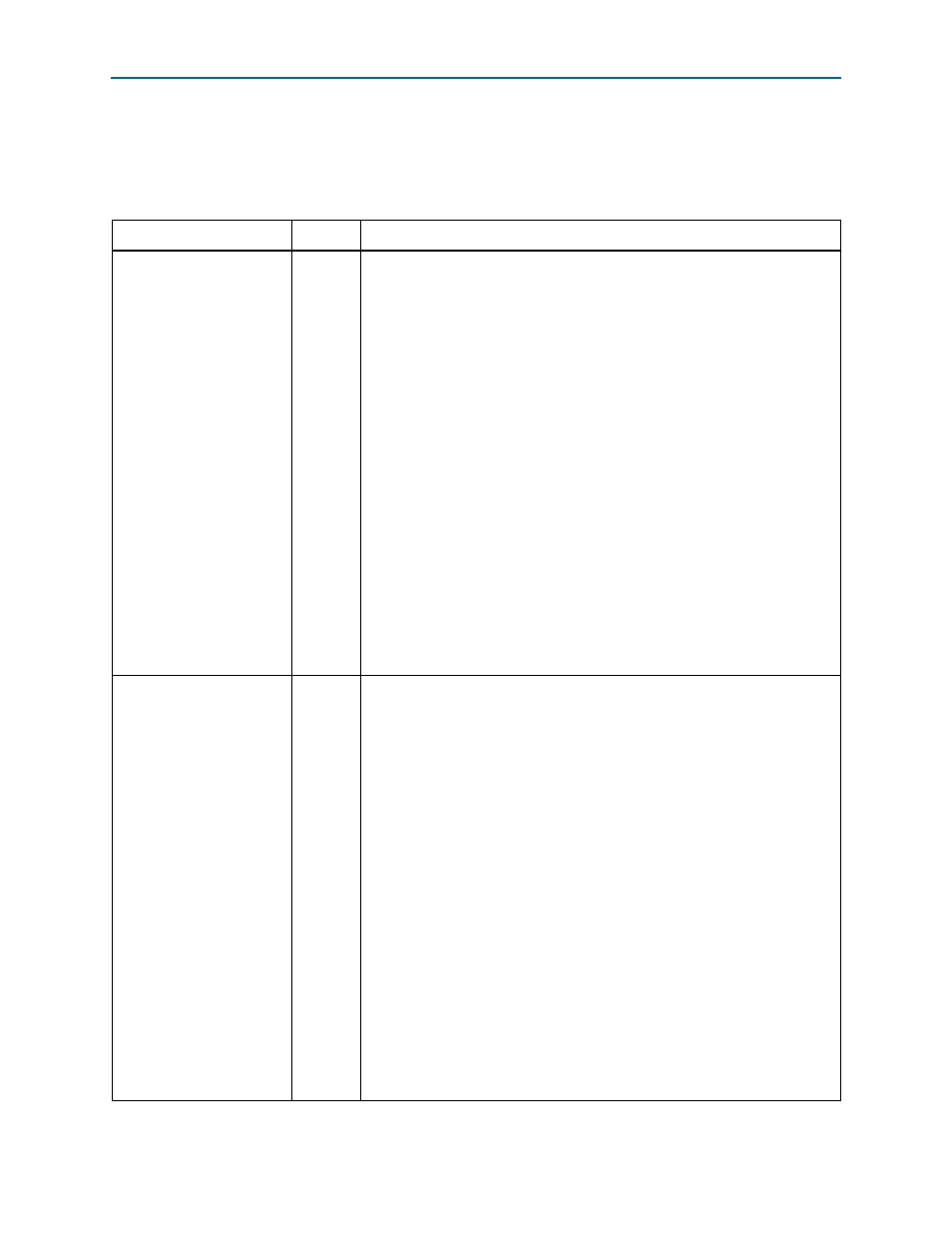

Table 5–1. Interlaken Data Interface Signals (Part 1 of 2)

Signal

Direction

Description

rx_serial_dataN_export

[M:0]

Input

Differential high-speed serial input data to the transceiver. It is connected to the

corresponding transmit data lines of the Interlaken link partner.

N corresponds to the HSIO bank number. N = 0 for 4-lane variations; N = {0,1} for

8- and 10-lane variations, N = {0,1,2} for 12-lane variations, and N = {0,1,2,3} for

20-lane variations. The width of the port is 4 (M=3) for 4-, 8-, and 12-lane

variations, and 5 (M=4) for 10- and 20-lane variations.

Lane 0 holds the MSB of the input data, which is input to the HSIO bank with the

highest number. Refer to

through

In an 8-lane variation, rx_serial_data1_export[3] connects to lane 0,

rx_serial_data1_export[2]

connects to lane 1, and so on;

rx_serial_data0_export[2]

connects to lane 5,

rx_serial_data0_export[1]

connects to lane 6, and

rx_serial_data0_export[0]

connects to lane 7.

In a 20-lane variation, rx_serial_data3_export[4] connects to lane 0,

rx_serial_data3_export[3]

connects to lane 1, and so on;

rx_serial_data2_export[4]

connects to lane 5,

rx_serial_data2_export[3]

connects to lane 6, and so on;

rx_serial_data1_export[4]

connects to lane 10;

rx_serial_data1_export[0]

connects to lane 14;

rx_serial_data0_export[4]

connects to lane 15, and

rx_serial_data0_export[0]

connects to lane 19.

tx_serial_dataN_export

[M:0]

Input

Differential high-speed serial output data from the transceiver. It is connected to

the corresponding receive data lines of the Interlaken link partner.

N corresponds to the HSIO bank number. N = 0 for 4-lane variations; N = {0,1} for

8- and 10-lane variations, N = {0,1,2} for 12-lane variations, and N = {0,1,2,3} for

20-lane variations. The width of the port is 4 (M=3) for 4-, 8-, and 12-lane

variations, and 5 (M=4) for 10- and 20-lane variations.

Lane 0 holds the MSB of the output data, which is output on the HSIO bank with

the highest number. Refer to

In an 8-lane variation, lane 0 is output on tx_serial_data1_export[3],

lane 1 is output on tx_serial_data1_export[2], and so on;

lane 5 is output on tx_serial_data0_export[2],

lane 6 is output on tx_serial_data0_export[1], and

lane 7 is output on tx_serial_data0_export[0].

In a 20-lane variation, lane 0 is output on tx_serial_data3_export[4],

lane 1 is output on tx_serial_data3_export[3], and so on;

lane 5 is output on tx_serial_data2_export[4],

lane 6 is output on tx_serial_data2_export[3], and so on;

lane 10 is output on tx_serial_data1_export[4];

lane 14 is output on tx_serial_data1_export[0];

lane 15 is output on tx_serial_data0_export[4], and

lane 19 is output on tx_serial_data0_export[0].