Altera Interlaken MegaCore Function User Manual

Page 75

Appendix B: Excluding Transceivers for Faster Simulation

B–3

External Transceiver Interface Clocks

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

1

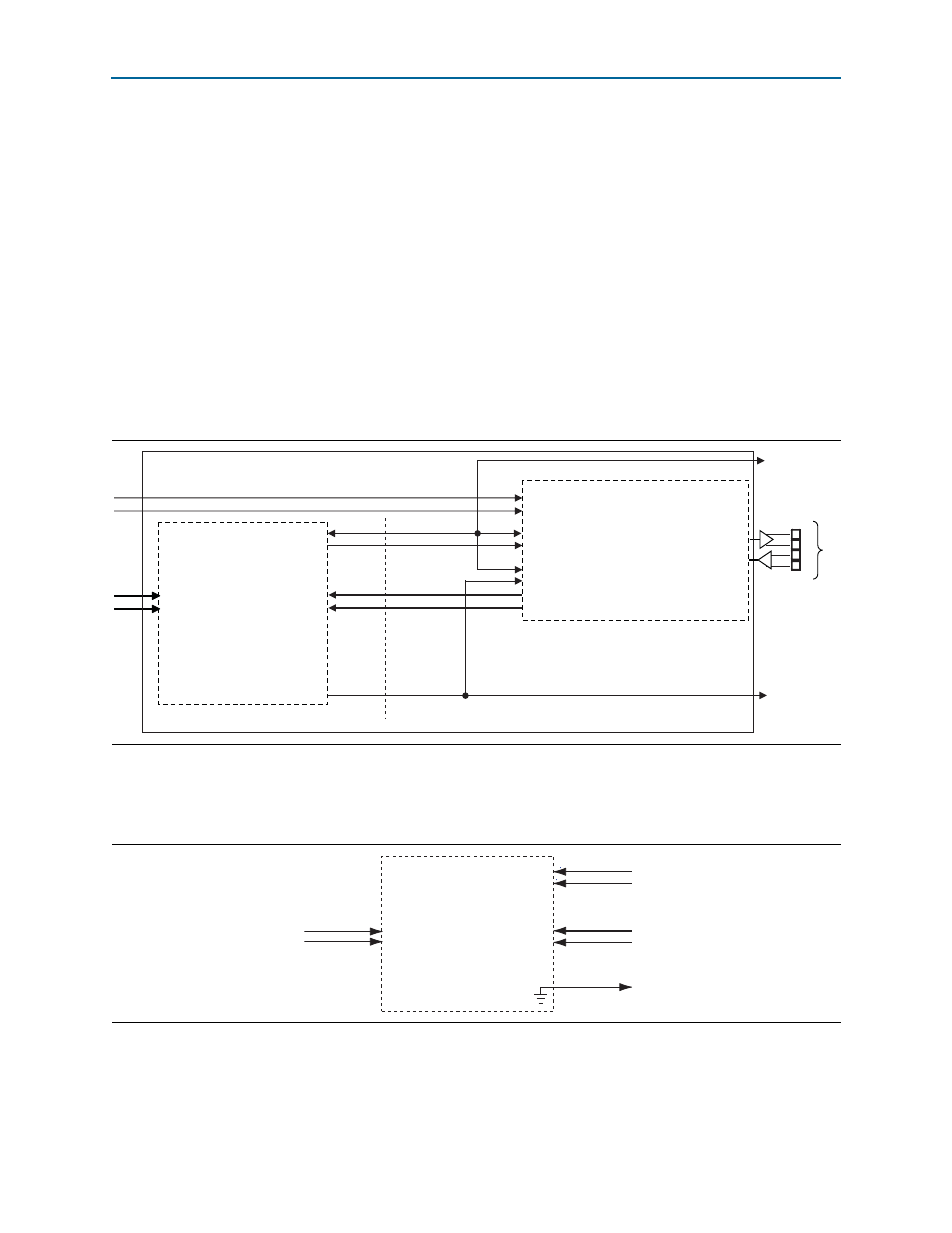

For all Interlaken MegaCore variations except the 8-lane, 3.125-Gbps variation, Altera

recommends that the same clock drive the rx_mac_c_clk, tx_mac_c_clk, and

tx_lane_c_clk

clocks.

Because the Interlaken MegaCore function does not include the high-speed

transceivers in this case, the ref_clk and cal_blk_clk input clocks to the transceivers,

which are input signals to the Interlaken MegaCore function if it includes

transceivers, are not included in the MegaCore function that excludes transceivers.

The reset controller is excluded from these variations because it runs on the

cal_blk_clk

clock, which is not available.

illustrates how you can derive the external transceiver interface signal and

clock information by simply removing the HSIO banks from the corresponding

variation with transceivers.

show the four-lane and

eight-lane variations without transceivers.

shows the clock diagram for a four-lane variation that does not include

transceivers.

Figure B–2. Clock Diagram for 4-lane Interlaken MegaCore Function with Transceivers

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

clk_out (master TX clock)

common_rx_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

tx_lane_clk

tx_data[79:0]

rx_data [79:0]

rx_lane_clk [3:0]

common_rx_coreclk

HSIO Bank 0

(low latency PCS mode)

tx_coreclkout

rx_coreclkout

x4

tx_mac_clk

rx_mac_clk

TX MAC and PCS

Exposed Interf

ace to

Tr

ansceiv

ers

RX MAC and PCS

Figure B–3. Clock Diagram for 4-lane Interlaken MegaCore Function Without Transceivers

tx_lane_clk

tx_data[79:0]

rx_data[79:0]

rx_lane_clk[3:0]

common_rx_coreclk

Interlaken

MegaCore Function

tx_mac_clk

rx_mac_clk