Altera DQ (ALTDQ) User Manual

Page 6

Page 6

Getting Started

DQ (ALTDQ) and DQS (ALTDQS) Megafunctions

November 2010

Altera Corporation

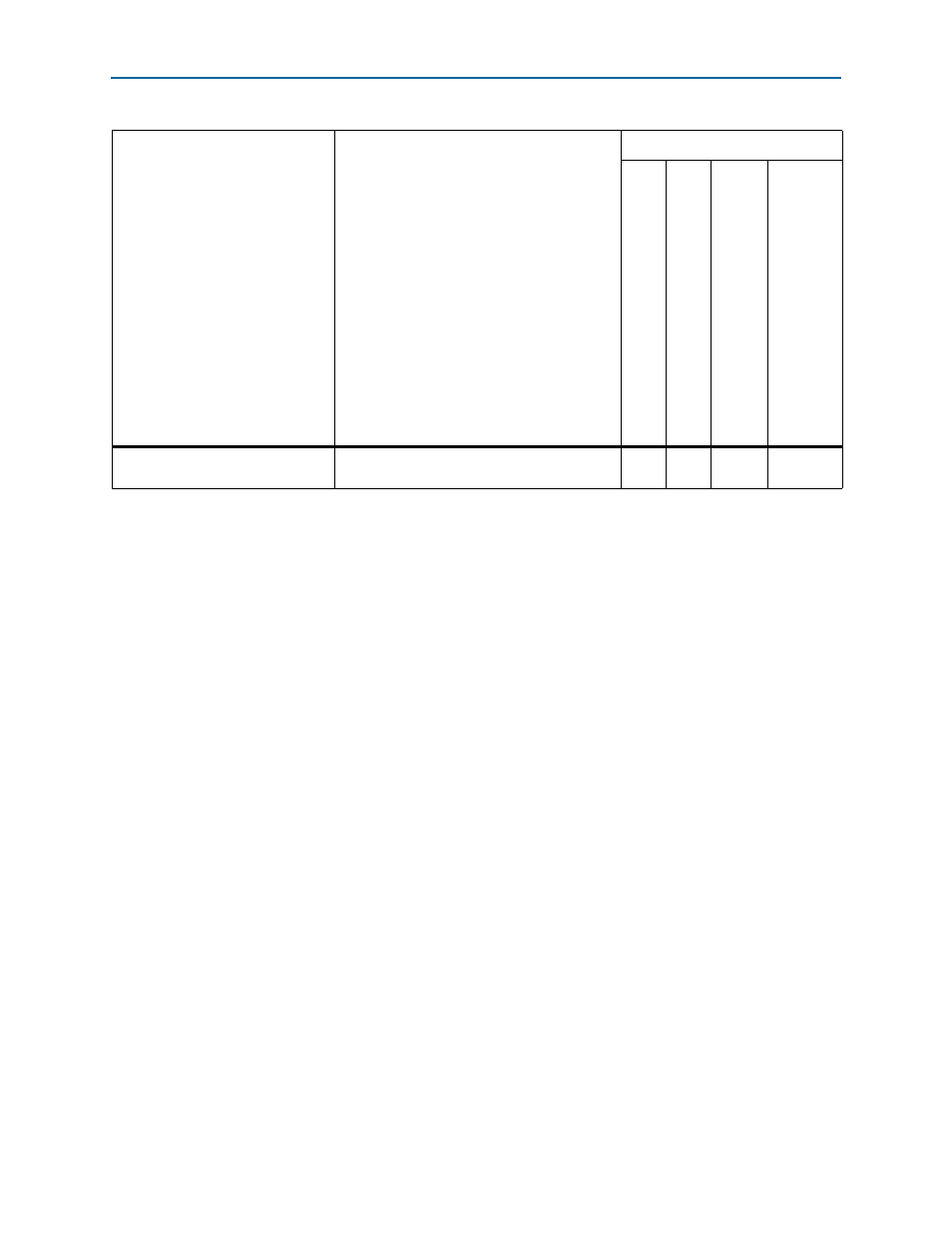

Invert dqs_padio port (when

driving output)

When you select this option, the dqs_padio

port is inverted, if driven as an output.

Yes

Yes

No

No

Notes to

:

(1) For supported DQS frequencies in these devices, refer to the “Cyclone II DDR Memory Support Overview”

chapter in volume 1 of the Cyclone II Device Handbook or the “Introduction” sectio

in volume 1 of the Cyclone III Device Handbook.

(2) For number of DQS/DQSn pair pins available in supported devices, refer to the

pter in volume

2 of the Arria GX Device Handbook,

chapter in volume 1 of the Cyclone II Device Handbook,

Cyclone III Device Handbook,

chapter in volume 2 of the Stratix Device Handbook, or th

chapter in volume 2 of the Stratix Device Handbook.

(3) The delay-locked loop (DLL) controls the delay chain settings to achieve a compensated delay for PVT. For example, you can use a DQS read

strobe or clock that is edge-aligned to its associated read data to clock the data into I/O registers if the data is delayed before reaching the

register. The DLL block computes the necessary delay settings by comparing the period of an input reference clock to the delay through an

internal delay chain. For more information about DLL, refer to the “DQS Phase-Shift Circuitry” se

chapter in volume 2 of the Stratix Device Handbook

chapter in volume 2 of the Stratix Device Handbook, and

chapter in volume 2 of the

Arria GX Device Handbook.

(4) For more information about the clock delay control block, refer to the “Clock Delay Control” sec

r in volume 1 of the Cyclone II Device Handbook.

(5) For Cyclone III, Cyclone III GX, and Cyclone III LS devices, you must use the "Input Delay from Dual-Purpose Clock Pin" assignment in the

Assignment Editor to set DQS clock delay.

(6) For more information about the DQS postamble circuitry, refer to the “DQS Postamble” section of the

in volume 1 of the Cyclone II Device Handbook.

Table 2. General Settings (Part 3 of 3)

Option

Description

Supported Devices

Cyclon

e

II

Cyc

lone

III, C

yclone

IV

GX

St

ratix, Strat

ix GX,

Stratix

II, Stratix

II

GX,

Arria

GX,

Ha

rdCopy

II