Vhdl library-use declaration, Ports and parameters – Altera DQ (ALTDQ) User Manual

Page 25

Ports and Parameters

Page 25

November 2010

Altera Corporation

DQ (ALTDQ) and DQS (ALTDQS) Megafunctions

VHDL LIBRARY-USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL

component declaration.

LIBRARY altera_mf;

USE altera_mf.altera_mf_components.all;

Ports and Parameters

This section describes all of the ports and parameters that are available for the ALTDQ

and ALTDQS megafunctions.

The parameter details are only relevant if you bypass the MegaWizard

Plug-In

Manager interface and use the megafunction as a directly parameterized instantiation

in your design. The details of these parameters are hidden if you use the MegaWizard

Plug-In Manager interface.

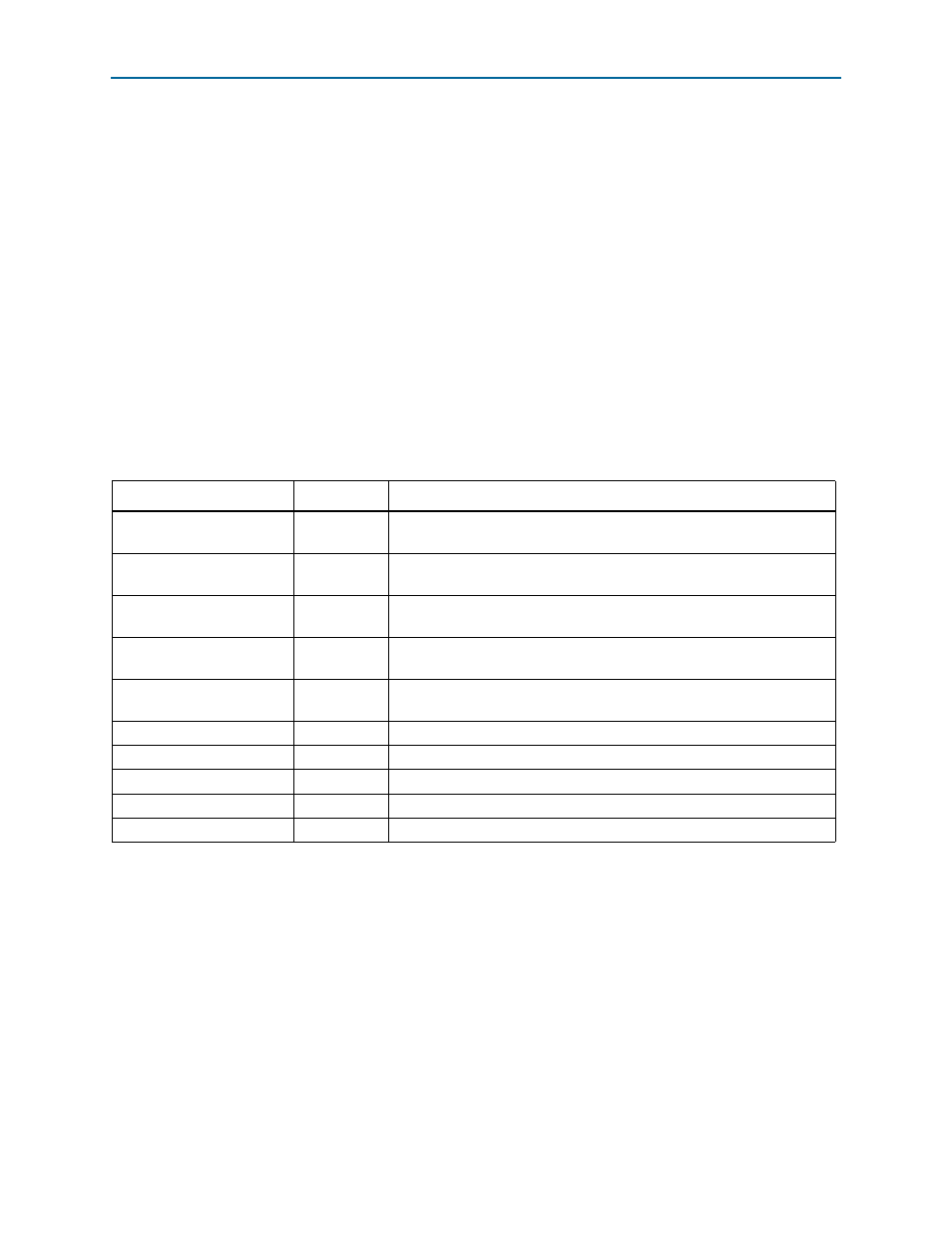

shows the input ports for the ALTDQ megafunction.

Table 12. ALTDQ Megafunction Input Ports

Port Name

Required

Description

aclr

No

Asynchronous clear input. If the aclr port is connected, the aset port

cannot be used.

aset

No

Asynchronous set input.If the aset port is connected, the aclr port

cannot be used.

datain_h[]

Yes

Data to be output to the padio port at the rising edge of the outclk signal.

The size of the port is dependent on the NUMBER_OF_DQ parameter.

datain_l[]

Yes

Data to be output to the padio port at the falling edge of the outclk

signal. The size of the port is dependent on the NUMBER_OF_DQ parameter.

ddioinclk

No

Clock input for the negative-edge input register. If omitted, the default is

GND

inclock

Yes

Clock input that drives the data strobe.

inclocken

No

Clock enable for the inclock port

oe

No

Output enable signal. The oe port defaults to V

CC

when enabled.

outclock

Yes

Clock signal for the output and oe registers.

outclocken

No

Clock enable signal for each clock port.

Note to

:

(1) Not available for Stratix and Stratix GX devices.