Altera DQ (ALTDQ) User Manual

Page 5

Getting Started

Page 5

November 2010

Altera Corporation

DQ (ALTDQ) and DQS (ALTDQS) Megafunctions

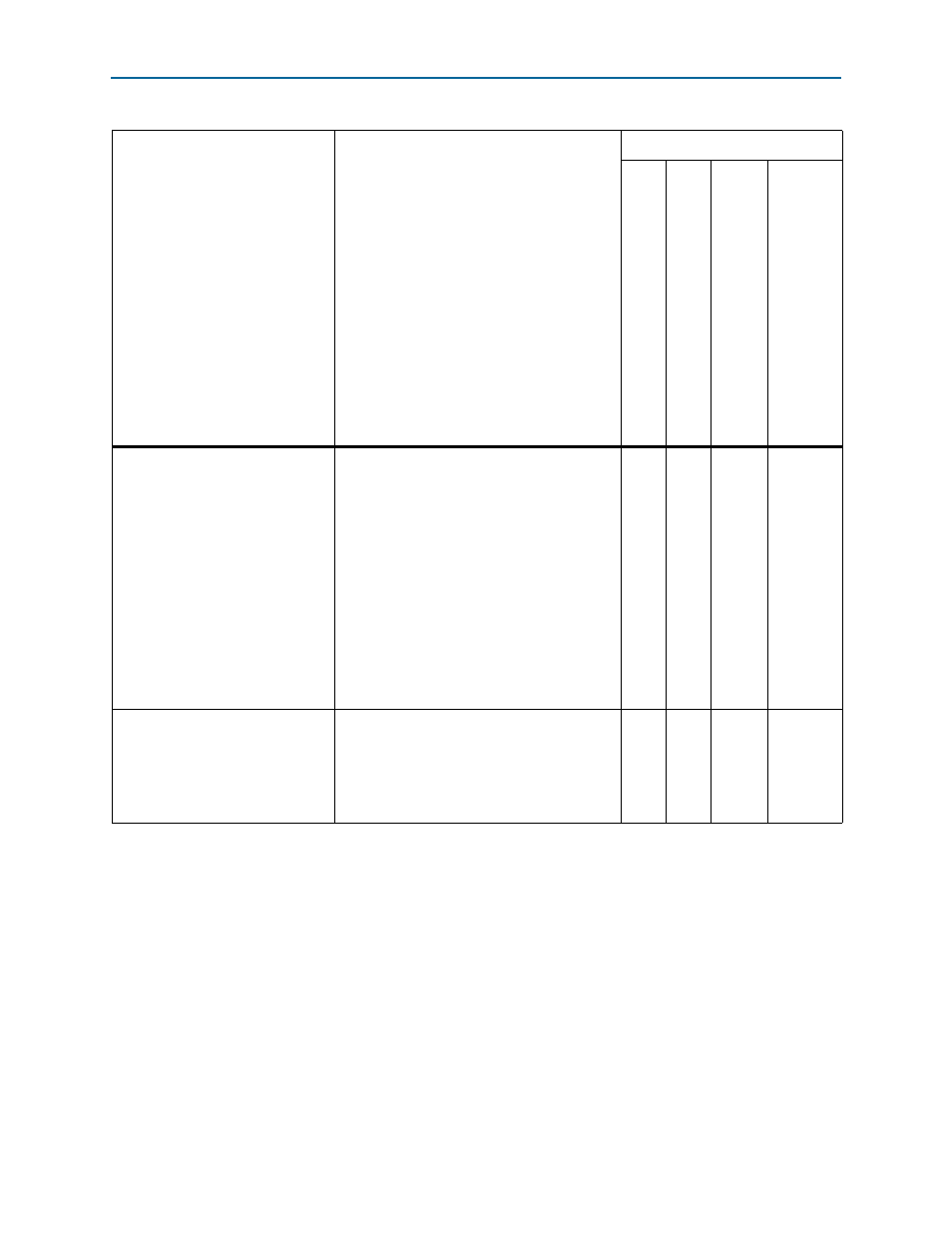

How should the delay chain be

specified?

This can be either a setting in ps or a value

from 0-63. This is the user-requested delay on

the clock delay control block. Delay is specified

either by number of delay buffers used or

desired time delay. Time delay is converted to

number of buffers during compilation. For the

actual buffer delay, refer to the respective

device data sheet.

These buffers have a fixed delay, which is not

dependent on input clock frequency clock delay

control circuit on each DQS pin allows a phase

shift that center-aligns the incoming DQS

signals within the data window of their

corresponding DQ data signals.

Yes

Yes

No

No

Allow DQS to be disabled during

read post-amble.

Inhibits the ddioinclk signal during read

postamble (when the DQS transitions from 0 to

Z). Stops the ddioinclk signal from creating

false clocks as the DQS goes to tristate. If

selected, adds an enable_dqs input port to

stop the ddioinclk signal.

Yes

Yes

No

No

Table 2. General Settings (Part 2 of 3)

Option

Description

Supported Devices

Cyclon

e

II

Cyc

lone

III, C

yclone

IV

GX

St

ratix, Strat

ix GX,

Stratix

II, Stratix

II

GX,

Arria

GX,

Ha

rdCopy

II