Altera DQ (ALTDQ) User Manual

Page 14

Page 14

Getting Started

DQ (ALTDQ) and DQS (ALTDQS) Megafunctions

November 2010

Altera Corporation

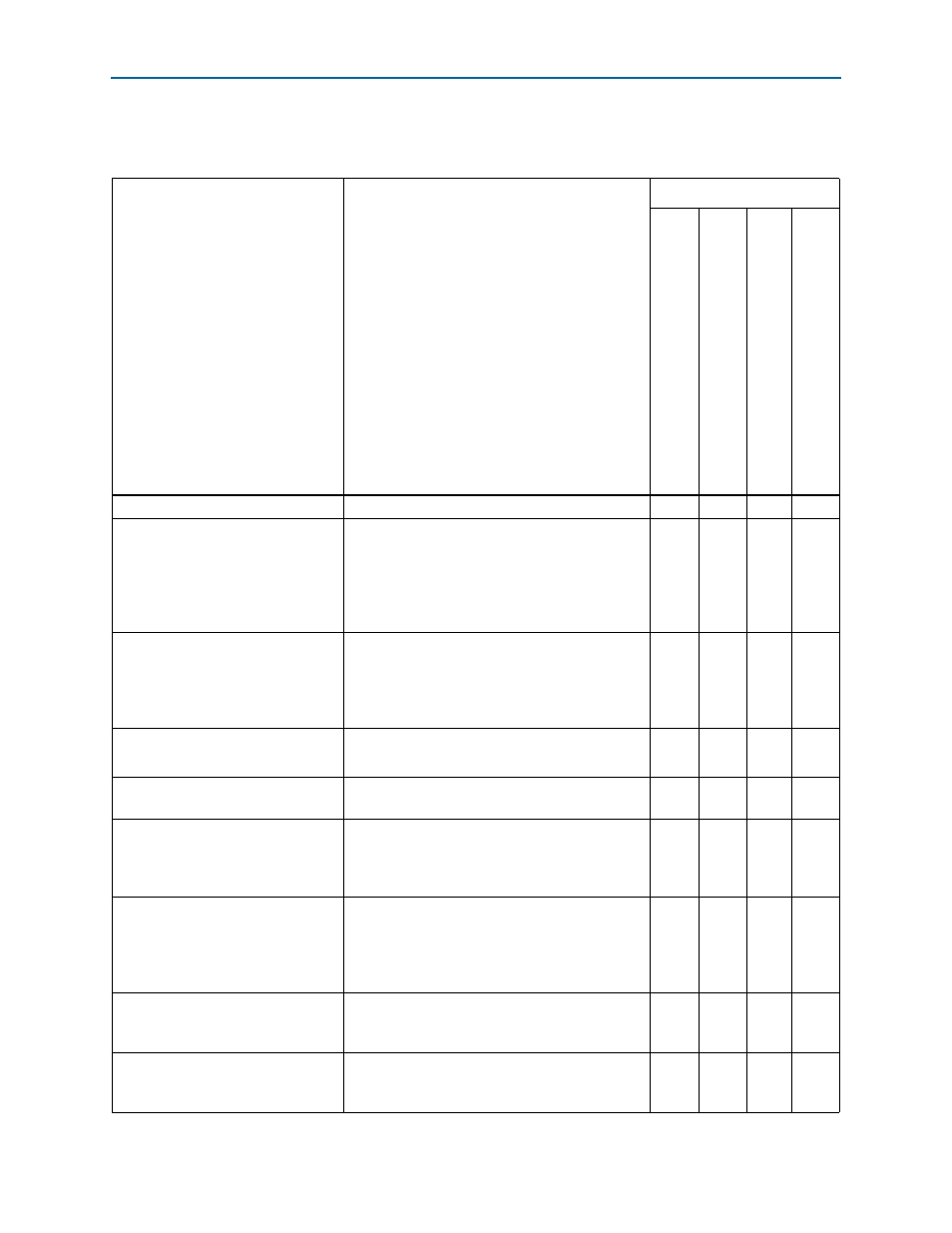

Page 3 of the ALTDQ parameter editor is the Parameter Settings page.

describes options available on page 3 of the ALTDQ megafunction.

Table 9. Parameter Settings

Option

Description

Supported Devices

Cy

clone

II

Cyclone

III, Cyclone

IV

GX

Str

a

tix, St

ratix GX,

Stra

tix

II,

Stratix

II

GX, Arria

GX, HardCopy

II

Currently selected device family

Specifies the Altera device family you are using.

Yes

Yes

Yes

Yes

How many DQ pins would you like?

Specifies the width of the data buses. If you are

using the Quartus II software version 6.0 or earlier,

this megafunction displays output ports as

dataout_h[]

and dataout_1[]; the Quartus II

software version 6.0 and later displays output

ports as dataout[] and dataout_ddio[].

Yes

Yes

Yes

Yes

Which asynchronous reset port

would you like?

You can use the asynchronous clear (aclr) or the

asynchronous preset (aset) as the asynchronous

reset. If you do not use either clear option, you

must specify whether the registers should power-

up high or low.

Yes

Yes

Yes

Yes

Create a clock enable port for each

clock port

Creates an input clock enable port (inclken) and

an output clock.

Yes

Yes

Yes

Yes

Create an output enable port

Creates an output enable port (oe) for this

instance of the ALTDQ instance.

Yes

Yes

Yes

Yes

Register output enable

Sets the OE_REGISTER_MODE parameter. When

enabled, a register is placed in the OE path and the

parameter is set to register. When disabled,

parameter defaults to NONE.

Yes

Yes

Yes

Yes

Delay switch-on by a half clock

cycle

Sets the EXTEND_OE_DISABLE parameter. When

enabled, the pin does not drive out until the falling

edge of the outclk signal. When enabled, the

parameter is set to TRUE, otherwise it defaults to

FALSE.

Yes

Yes

Yes

Yes

Invert Input Clock

If enabled, the first bit of data is captured on the

rising edge of the input clock; if not enabled, it is

captured on the falling edge of the input clock.

Yes

Yes

Yes

Yes

Use ddioinclk port (from DQSn bus)

Creates a ddioinclk port. This port clocks the

negative edge triggered input/capture register of

the ALTDQ instance.

Yes

Yes

Yes

Yes