Altera DQ (ALTDQ) User Manual

Page 17

Design Example: Implement DDR I/O Interface

Page 17

November 2010

Altera Corporation

DQ (ALTDQ) and DQS (ALTDQS) Megafunctions

The ALTDQ module is generated. The next section shows you how to create an

ALTDQS megafunction.

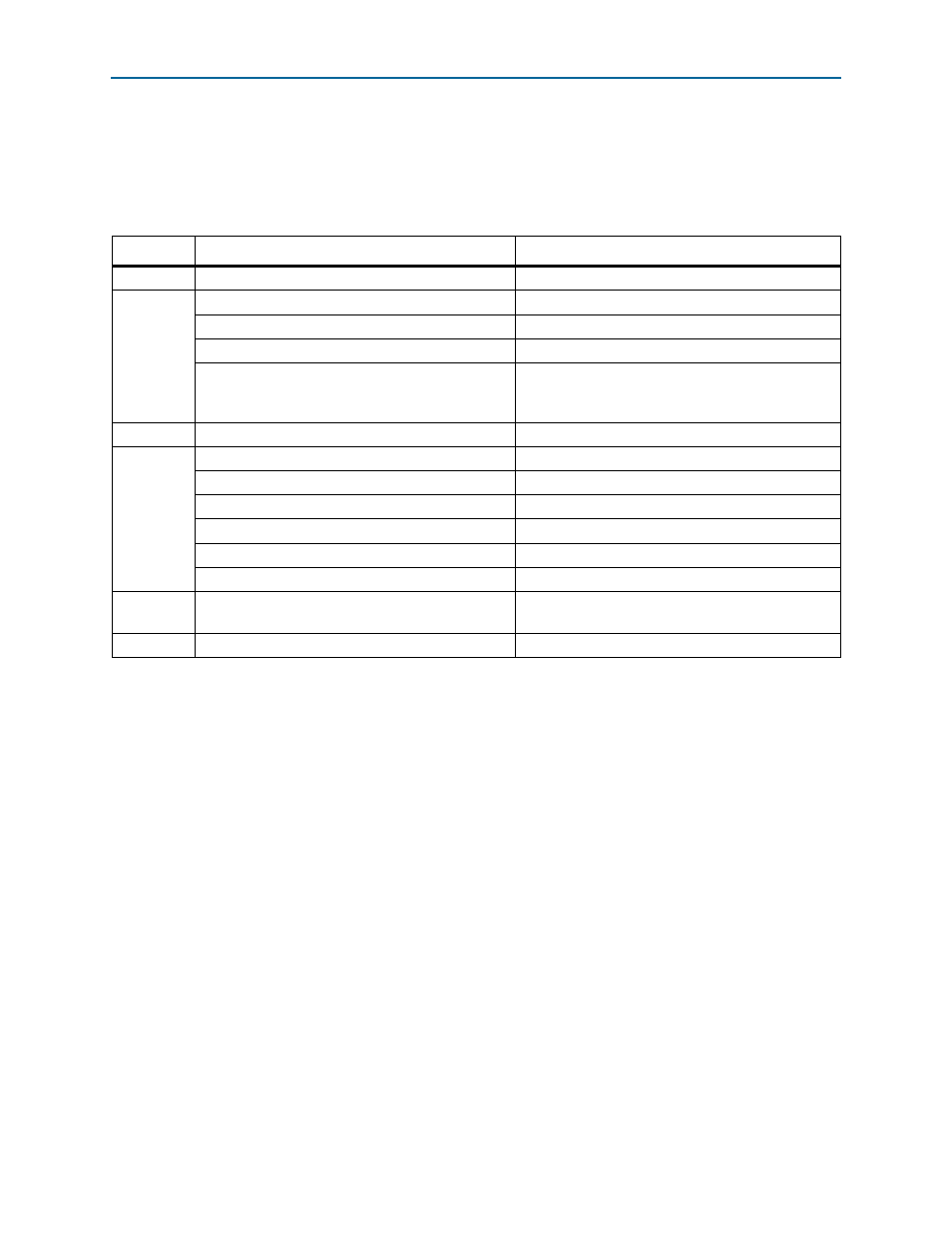

shows the MegaWizard Plug-In Manager page options and description you

should select to create the example ALTDQS megafunction.

Page 7 of the MegaWizard Plug-In Manager lists the simulation model file needed to

properly simulate the generated design files. No further input is needed. Perform

these steps to continue creating an ALTDQS megafunction:

1. Turn on the Instantiation template file and Verilog 'Black Box' declaration file

options.

2. Turn off the AHDL Include file, VHDL Component declaration file, and Quartus

symbol file

options.

3. Click Finish.

The ALTDQS module is generated.

Combine ALTDQ and ALTDQS Modules to Create a DDR I/O Interface

This section describes how to create a new top-level Verilog HDL file that combines

the ALTDQ and ALTDQS modules.

1. With the dq_dqs_ex.qar project open, open the dq_dqs_ex.v file.

2. Verify that the DQ and DQS functions are correctly connected in the top-level

dq_dqs_ex.v

file (refer to

).

3. On the Project menu, click Add/Remove Files in Project. The Settings window

appears.

Table 11. Parameter Settings for ALTDQS Megafunction

Page

Option

Description

1

Which action do you want to perform?

Select Create a new custom megafunction variation

2a

Select a megafunction from the list below

Select ALTDQS from the I/O category

Which device family will you be using?

Select Cyclone II

Which type of output file do you want to create?

Select Verilog HDL

What name do you want for the output file?

Browse to the folder dq_dqs_ex_1.0_restored. Name

the file dqs. (If asked if it is okay to overwrite an

existing file, click OK)

3

How many DQS pins would you like?

Select 1

4

What is the frequency of the DQS input(s)?

Select

133.333 MHz

Create an output enable port

Turn on option

Register the output enable

Turn off option

How should the delay chain be specified?

Select

As delay chain setting and

select

50

Allow DQS to be disabled during read post-amble

Turn off option

Invert ‘dqs_padio’ port (when driving output)

Turn off option

5

What effect should the ‘dqs_areset’ port have on

output registers?

Select

Clear

6

How do you want to use the ‘dqsn_padio’ port?

Select

Not Used