Echelon LonTal Stack User Manual

Page 49

LonTalk Stack Developer’s Guide

37

• 8 data bits (least-significant bit first)

• 1 stop bit

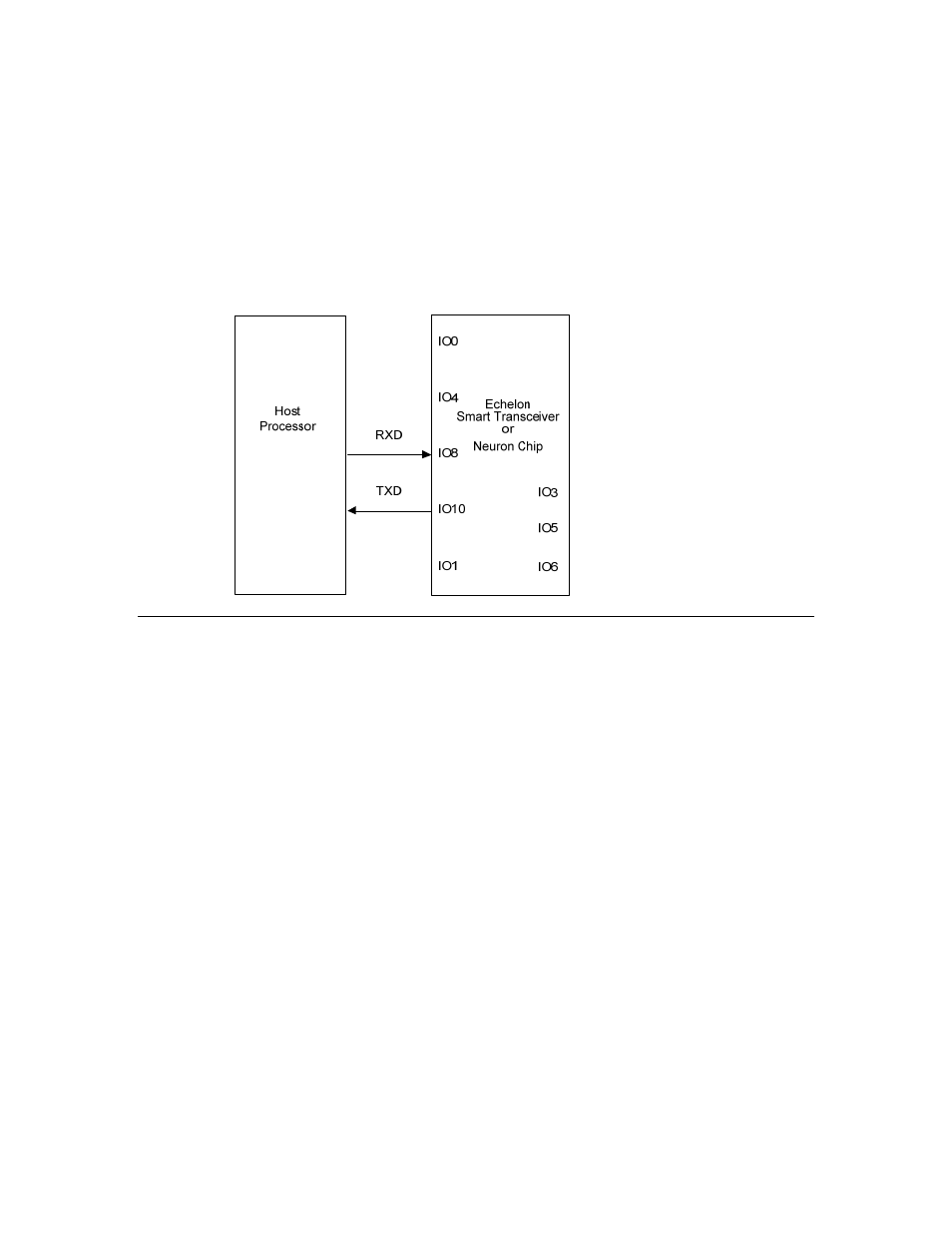

The SCI link-layer interface uses two serial data lines: RXD (receive data) and

TXD (transmit data). The following diagram summarizes the two serial data

lines and their I/O pin assignments. The signal directions are from the point of

view of the Echelon Smart Transceiver. An uplink transaction describes data

exchange from the Echelon Smart Transceiver to the host processor, and uses the

TXD line. A downlink transaction refers to data exchange from host processor to

the Echelon Smart Transceiver, and uses the RXD line.

Performing an Initial Echelon Smart Transceiver

Health Check

After you load the Layer 2 MIP image into an Echelon Smart Transceiver or

Neuron Chip, the Echelon Smart Transceiver or Neuron Chip enters quiet mode

(also known as flush mode). While the Echelon Smart Transceiver or Neuron

Chip is in quiet mode, all network communication is paused.

The Echelon Smart Transceiver or Neuron Chip enters quiet mode to ensure that

only complete implementations of the LonTalk protocol stack attach to a

L

ON

W

ORKS

network. In a functioning LonTalk Stack device, the application

initializes the Echelon Smart Transceiver or Neuron Chip. After that

initialization is complete, the Echelon Smart Transceiver or Neuron Chip leaves

quiet mode and enables regular network communication.

To check that the Echelon Smart Transceiver or Neuron Chip is functioning

correctly before the host processor has initialized it, you can use an oscilloscope

or a logic analyzer to observe the activity on the TXD (IO10) pin that reflects the

uplink LonNiReset message transfer that follows an Echelon Smart Transceiver

or Neuron Chip reset, as shown in the following figure.