Echelon FTXL Hardware User Manual

Page 82

74

Using the Bring-Up Application to Verify FTXL Hardware Design

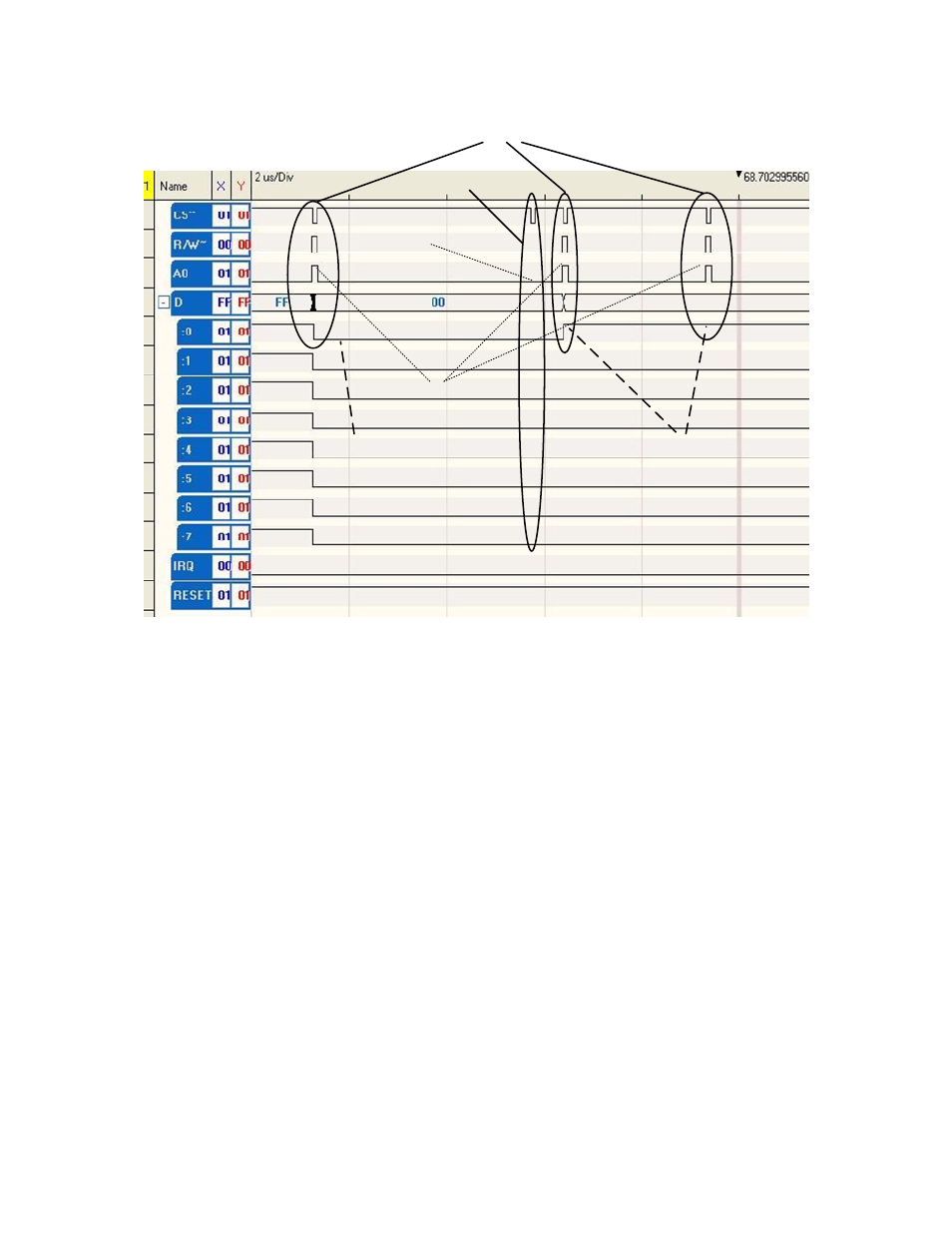

Read Handshake

Write length = 0

Handshake (D0)

busy

Handshake (D0)

ready

A0 low -> D0 is

data

A0 high -> D0

is handshake

Figure 30. Writing the Length Byte (0x00)

The CS~ signal is asserted (low) every time a byte operation is in progress. The

R/W~ signal is asserted (low) on a write, and deasserted (high) on a read. To

read the handshake (or status) register, the A0 signal is deasserted (high), in

which case D0 is the handshake signal. If A0 is asserted (low), the D0 signal is

the least significant data bit. The diagram shows the following four operations:

• Read status (CS~ low, R/W~ high, A0 high). The status register (D0) is

ready.

• Write data byte with value 0x0 (CS~ low, R/W~ low, A0 low, D0-D7 =

0x00).

• Read status (CS~ low, R/W~ high, A0 high). The status register (D0) is

busy.

• Read status (CS~ low, R/W~ high, A0 high). The status register (D0) is

busy.

Figure 31 on page 75 shows the state of the signals when the host passes the

token to the FTXL Transceiver. This process consists of the following steps:

1. Read the status register and determine that the FTXL Transceiver is

ready.

2. Write the length byte (0x00).

3. Repeatedly read the status register until the FTXL Transceiver is ready.

4. Write the token byte (0x00).