Echelon FTXL Hardware User Manual

Page 67

FTXL Hardware Guide

59

e. If necessary, modify the assigned IRQ number for the component;

see

Addressing, Size, and IRQ Requirements

on page 49 for

recommendations about the IRQ assignments.

10. Add the FTXL Transceiver Reset component:

a. Expand the FTXL folder.

b. Select FTXL Transceiver Reset.

c. Click Add to open the MegaWizard for the component.

d. In the MegaWizard for the FTXL Transceiver Reset, there are no

parameters to set. Click Finish to add the component to the

design.

11. If necessary, set the base addresses of the newly added components.

Altera recommends that you let the SOPC Builder tool assign addresses:

select System → Auto-Assign Base Addresses.

12. Edit the Avalon MM-Tristate Bridge component for the FTXL Parallel I/O

Transceiver Interface component to verify that none of the signals are

shared:

a. Right-click the tristate_bridge component and select Edit to open

the MegaWizard for the Avalon MM-Tristate Bridge.

b. Verify that the bridge is registered on the Incoming Signals page.

c. Verify that none of the signals for

FTXL_PIO_inst.avalon_tristate_slave_0 are selected on the

Shared Signals page.

d. Click Finish to close the MegaWizard for the Avalon MM-Tristate

Bridge.

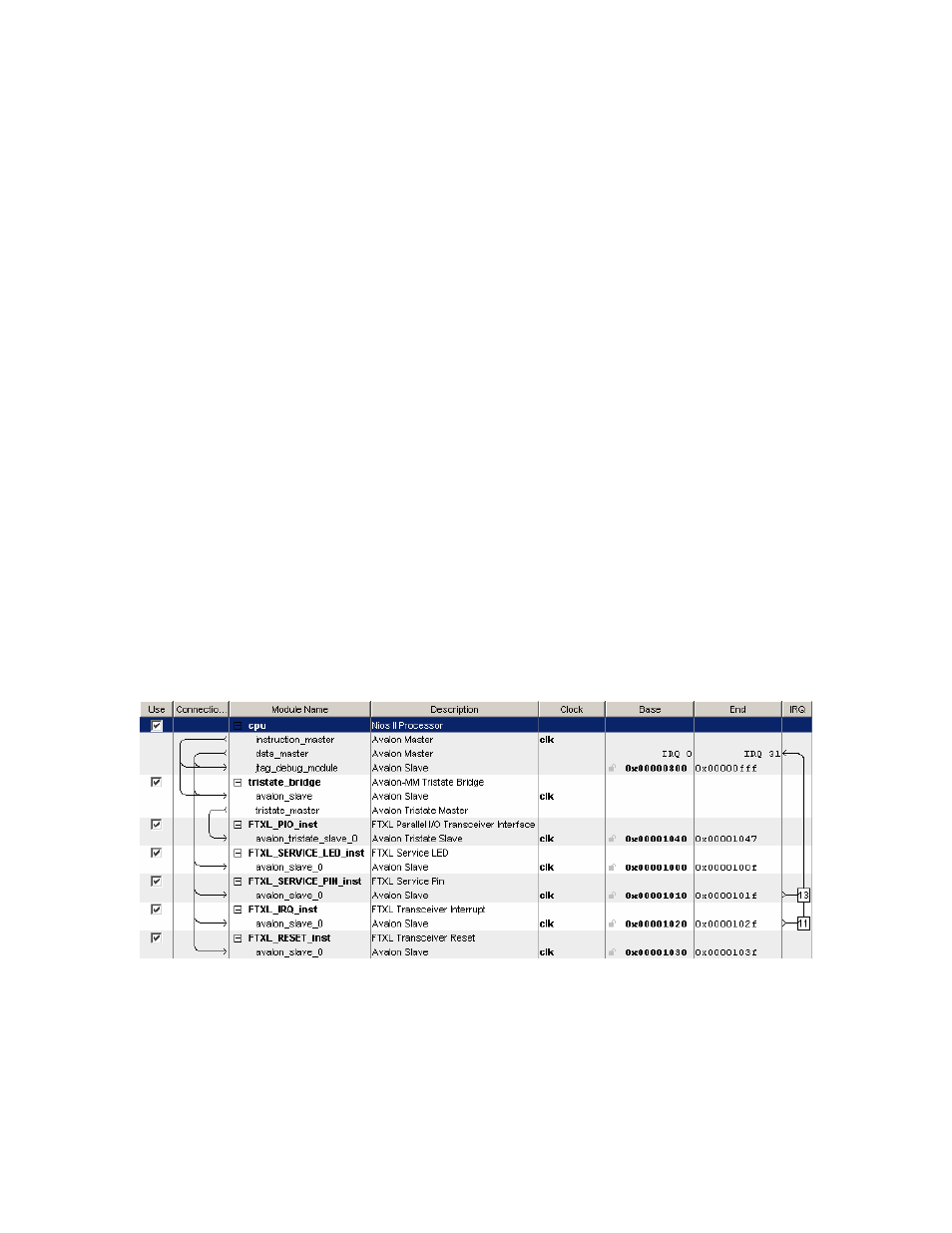

After you add the FTXL components, the design should look similar to Figure 23.

Figure 23. FTXL Components Added to the SOPC Builder Design

When you are satisfied with the SOPC Builder design, you must regenerate it:

click Generate at the bottom of the SOPC Builder window.