Figure 28, 72 sh – Echelon FTXL Hardware User Manual

Page 80

72

Using the Bring-Up Application to Verify FTXL Hardware Design

Read Status (Busy)

Host asserts reset

Host deasserts reset

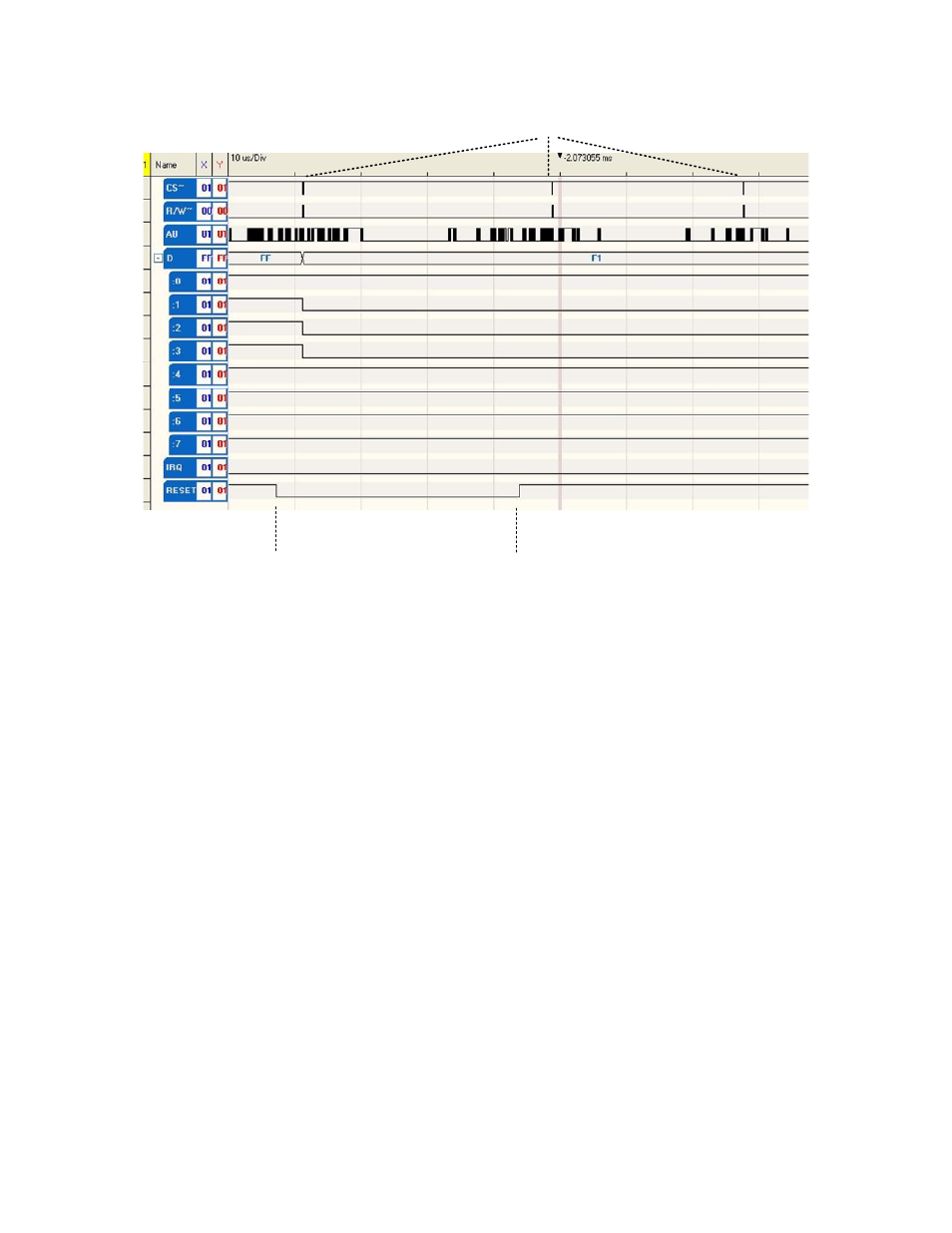

Figure 28. Host Asserts and Deasserts Reset and Checks Status

Figure 29 on page 73 shows the detail of the first read status from Figure 28.

The figure shows the CS~, R/W~, A0, and HS signals just after the reset line has

been asserted, and the host reads the status register. When CS~ is asserted

(low), a byte transfer is in progress. R/W~ controls whether the transfer is a read

or a write. In this case, R/W~ is deasserted (high), which indicates that this

transfer is a read. The A0 signal controls whether the D0 signal should report

the handshake (status) or the least significant bit of the data. In this case A0 is

high, which indicates that D0 represents the handshake signal.