Echelon FTXL Hardware User Manual

Page 40

32

FTXL Transceiver Hardware Interface

Control Flow: Host Sending Data to the FTXL

Transceiver

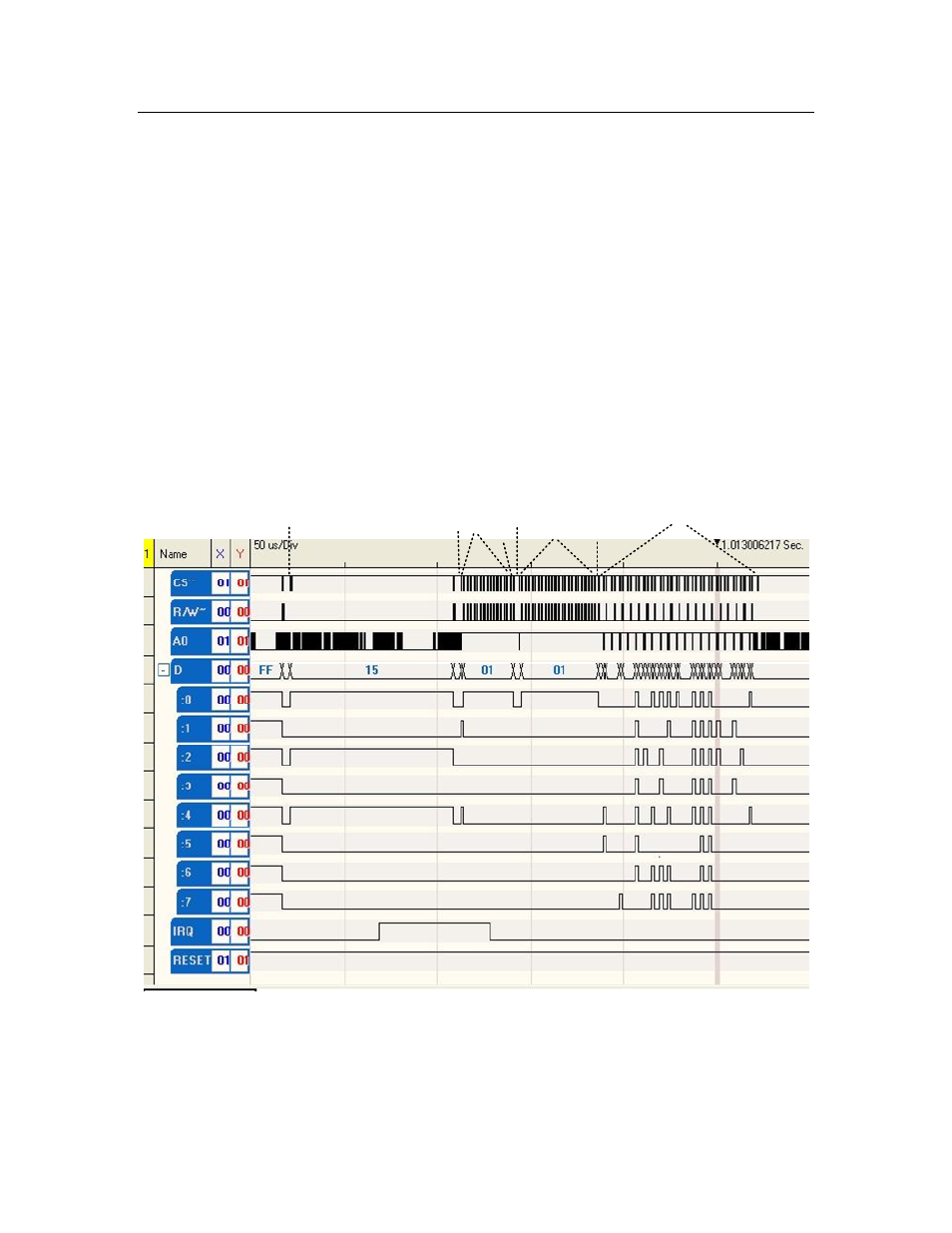

When the host program is ready to send a downlink message to the FTXL

Transceiver, it asserts the A0 pin. It receives the write token after the

transceiver has sent a complete message, or passed a null token. The transceiver

asserts IRQ after it has received the first byte of the message (the length byte),

and is ready to receive the rest of the bytes (in fast-I/O mode). It does not assert

IRQ if the host sends the null token.

Note: The transceiver never holds onto the token; when it gets the token, it

either writes a message or passes the token back to the host.

Figure 12 shows an overview example logic analyzer trace of the timing control

flow when the host sends data to the FTXL Transceiver. In this example, the

host sends a service-pin message.

See Appendix A,

Using the Bring-Up Application to Verify FTXL Hardware

, on page 63, for more detailed information about verifying the

communications between the host processor and the FTXL Transceiver.

Write

length

Write 1

st

data byte

Write 2

nd

data byte

Write remaining

bytes

Busy

Ready

Busy

Ready

Figure 12. Overview Timing Diagram: Host Sends Data to the FTXL Transceiver

Figure 13 on page 33 shows a more detailed timing diagram for writing the

length byte for the service-pin message. The diagram also shows the read

handshake.