Return stack – Echelon Neuron User Manual

Page 33

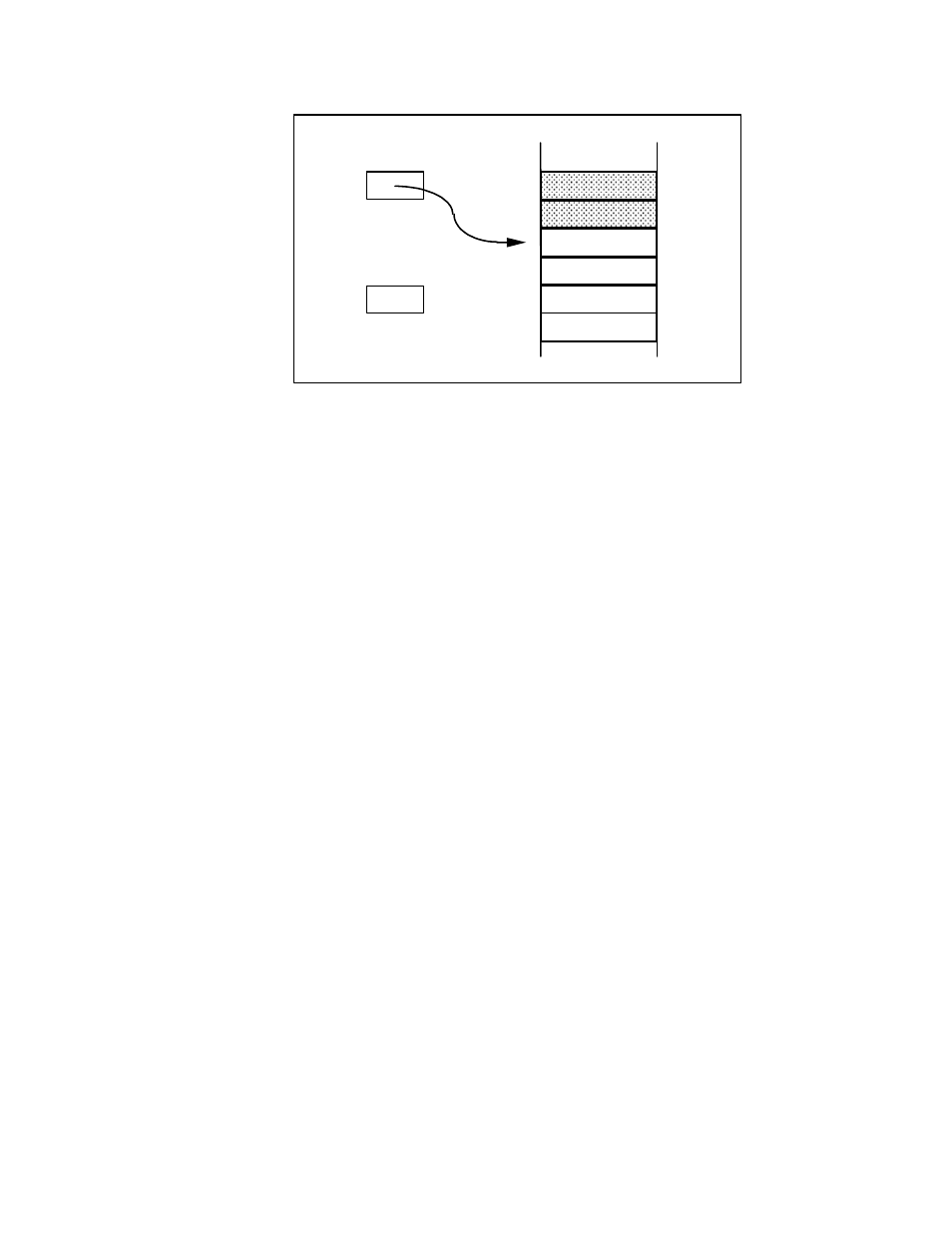

DSP

TOS

1

2

3

4

5

Low

High

NEXT

Figure 3. The Data Stack after a Push

For two-byte quantities, a two-byte push places the most-significant byte (MSB)

onto the stack first, followed by the least-significant byte (LSB).

Some assembly instructions support the DSP-relative addressing mode, which

provides easy access to the eight bytes of data in the stack below NEXT

(expressed with their negative DSP-relative offset -1..-8).

Return Stack

The return stack is also located in base page RAM. It consists of one register and

associated memory. The return stack pointer (RSP) is an 8-bit address register

that is added to the BP to address the top of the return stack. The RSP grows

towards lower addresses.

When calls are executed, the address of the next sequential instruction is stored

on the top of the return stack. This is a 16-bit address stored with the least

significant byte first (that is, the high order byte is pushed last).

Example: If a call were executed from location H'0124, the contents of the

return stack would be as shown in Figure 4.

Neuron Assembly Language Reference

23