Nop (no operation) – Echelon Neuron User Manual

Page 101

NOP (No Operation)

The NOP instruction performs no operation. The NOP instruction uses the

implicit addressing mode. This instruction is a one-byte instruction that takes up

space and CPU cycles, but does not affect the processor.

Note that this instruction is equivalent to a minimum short branch (forward one

byte): SBR *+1.

The NOP instruction applies to Series 3100, 5000, and 6000 devices.

Syntax:

The NOP instruction requires no operands:

NOP

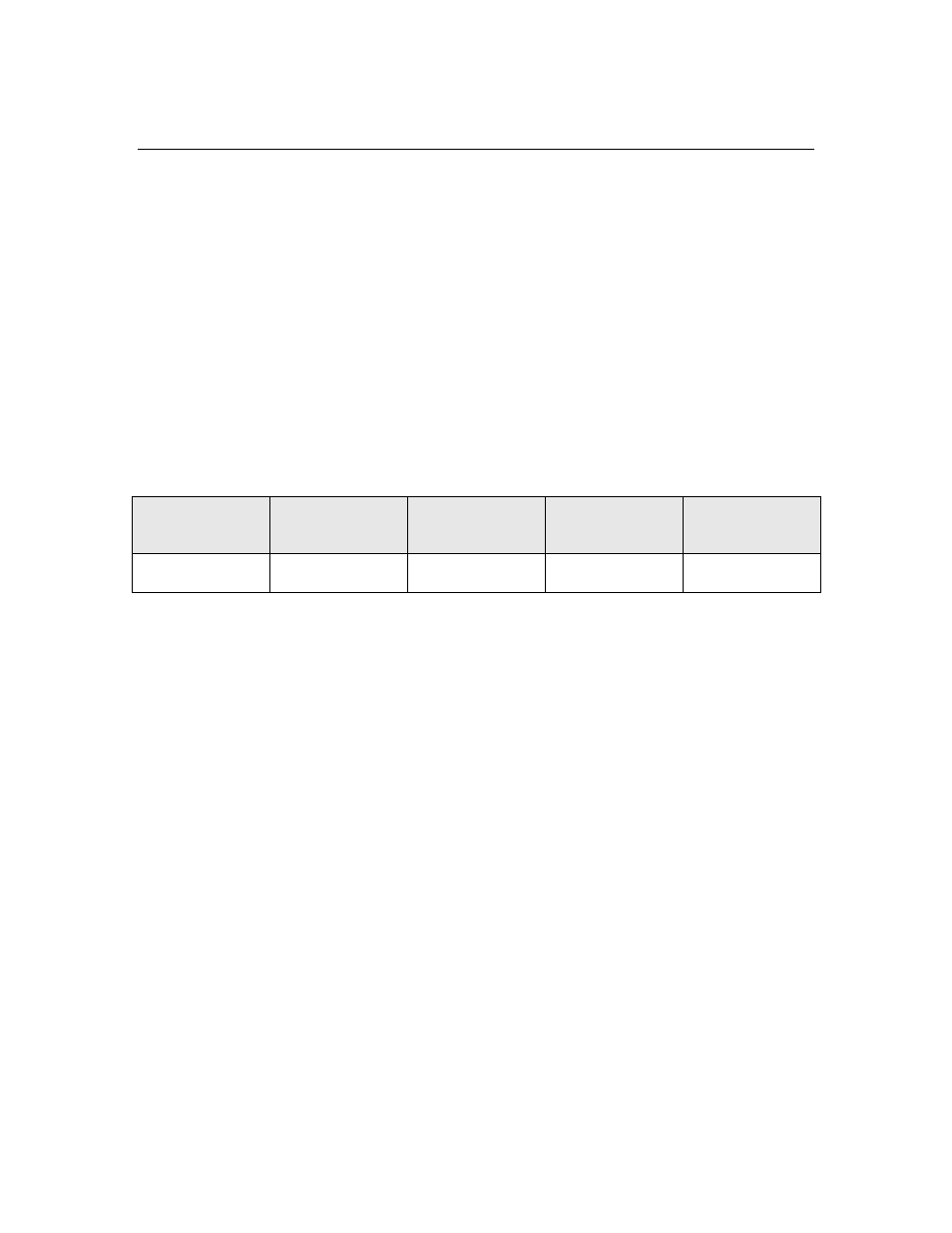

Table 34 describes the attributes of the NOP instruction.

Table 34. NOP Instruction

Instruction

Hexadecimal

Opcode

Instruction

Size (Bytes)

CPU Cycles

Required

Affect on

Carry Flag

NOP

20

1

1

None

Example:

The following example uses the NOP instruction to adjust the timing cycles

required for a specific function. The function causes a delay of 22*count+9 cycles

(not including the initial call to the function). The function assumes that the

count value is already on the data stack.

delay_22n_cycles APEXP

poppush ; () [count]

delay_22n_loop

pushd [msg_p]

popd [msg_p]

rolc

rorc

nop

dbrnz delay_22n_loop

ret ; return to caller

Neuron Assembly Language Reference

91