Echelon Neuron User Manual

Page 212

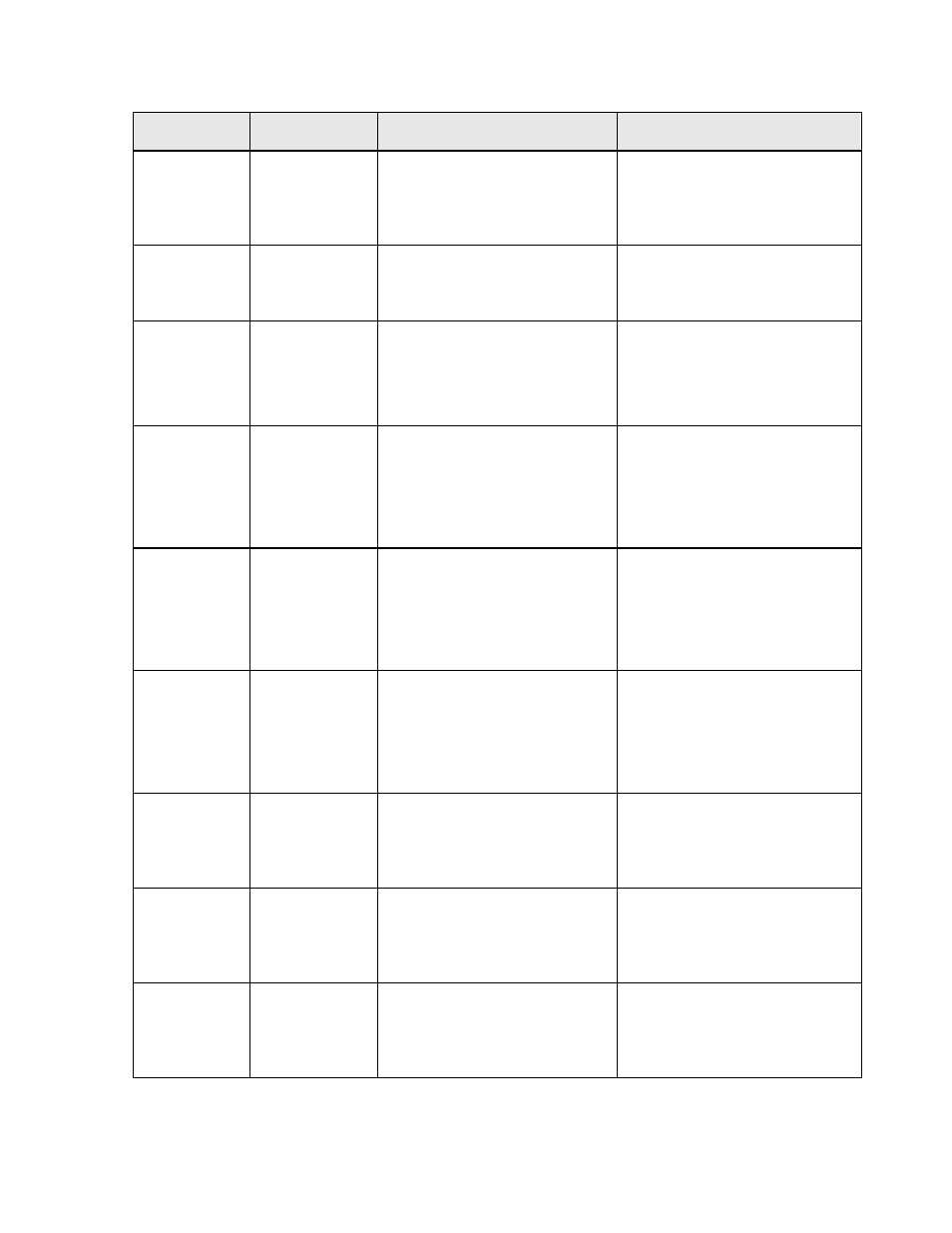

Mnemonic

Operand

Operation

Description

PUSH

[PTR] [D]

[++DSP] = TOS

TOS = [[BP+(PTR*2)]+D]

IP = IP+2

Pushes 8-bit value at address

held in 2-byte pointer PTR plus

displacement D (from 0 to 255)

onto TOS.

PUSH

[PTR] [TOS]

[++DSP]=[[BP+(PTR*2)]+TOS]

IP = IP+1

Pushes 8-bit value at address

held in 2-byte pointer PTR plus

TOS onto NEXT.

PUSH

CPUREG

[++DSP] = TOS

TOS = CPUREG

IP = IP+1

Pushes 8-bit value in specified

register onto TOS.

CPUREG = FLAGS, RSP, DSP,

TOS, NEXT

PUSHD

#literal8_1,

#literal8_2

[++DSP] = TOS

[++DSP] = #literal8_1

TOS = #literal8_2

IP = IP+3

Pushes 2 eight-bit literals onto

data stack.

PUSHD

#literal16

[++DSP] = TOS

[++DSP] = MSB(literal16)

TOS = LSB(literal16)

IP = IP+3

Pushes one 16-bit constant

onto data stack.

PUSHD

[PTR]

[++DSP] = TOS

[++DSP] = [BP + (PTR * 2)]

TOS = [BP + (PTR * 2) + 1]

IP = IP+1

Push content of pointer PTR (2

bytes) onto data stack.

PUSHPOP

[++DSP] = TOS

TOS = [++RSP]

IP = IP+1

Pops 8-bit value from top of

return stack and pushes it onto

TOS.

PUSHS

#literal

[++DSP] = TOS

TOS = literal

IP = IP+1

Pushes literal value from 0 to 7

onto the data stack.

RET

IPH= [++RSP]

IPL = [++RSP]

IP= IP+1

Return from function.

202

Neuron Assembly Instructions Listed by Mnemonic