Echelon Neuron User Manual

Page 30

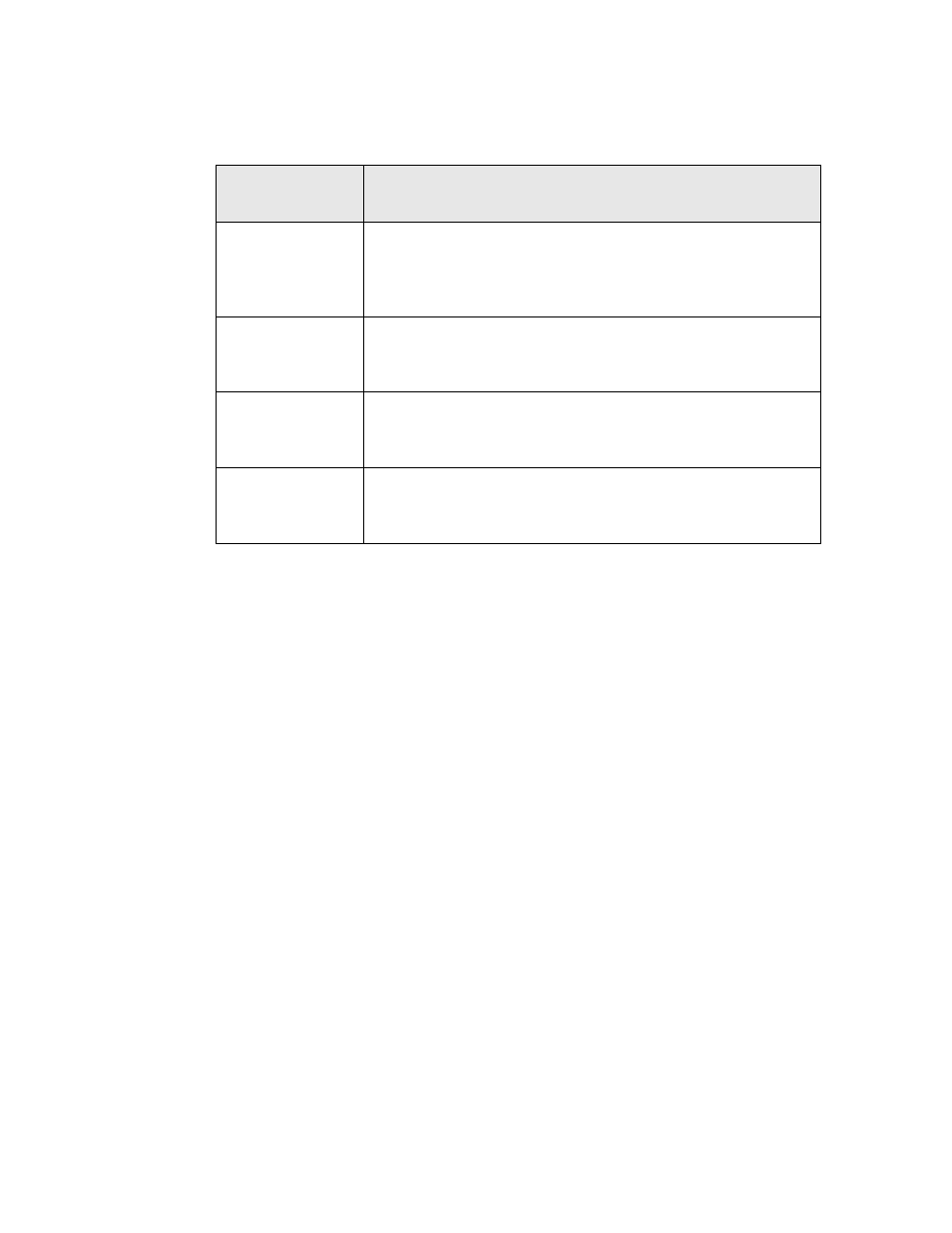

Table 7. Pointer Registers

Pointer

Register

Description

P0

Scratch register. A function can use this register as needed.

Assume that any call to the firmware, or to any function in a

library or written in Neuron C, might change the contents of

this register.

P1

Always points to the beginning of the RAMNEAR segment.

Do not change this register’s content when working in a

Neuron C context.

P2

Used by Neuron C programs. Assume that any call to the

firmware, or to any function in a library or written in

Neuron C, might change the contents of this register.

P3

Scratch register. Assume that any call to the firmware, or to

any function in a library or written in Neuron C, might

change the contents of this register.

A scratch register is one that can be used for temporary data storage by multiple

programs or functions. That is, must typically be saved before and restored after

calling any other function.

Important: Do not modify P1 or P2 in your Neuron assembly functions.

The Neuron Assembly language refers to the general-purpose pointer registers by

their numerical identifier, 0..3. A typical assembly language function defines the

mnemonics P0 to P3 for these registers by using the EQU assembly directive.

Example: The following push instruction uses indirect-relative addressing.

This addressing mode addresses the argument through two operands: a pointer

register and an offset. The effective address of the operation’s argument is

obtained by adding the offset to the contents of the pointer register.

The following instruction pushes the 7th byte from the memory address pointed

to by the P0 register onto the data stack:

push [0][7]

Defining mnemonic names for the general-purpose registers makes this

instruction more easily readable. The following example is equivalent to the

previous one:

P0 EQU 0

push [P0][7]

However, because you define the P0 mnemonic, it carries no special meaning for

the Neuron Assembler. The Assembler does not validate that the mnemonic

refers to the correct or intended register.

For the purpose of clarity (and unless explicitly mentioned to the contrary), all

source code examples in this book assume that the following mnemonics are

defined:

20

Neuron Architecture for Neuron Assembly Programming