Pushd (push pointer direct) – Echelon Neuron User Manual

Page 117

PUSHD (Push Pointer Direct)

The PUSHD instruction pushes two bytes from the specified location into TOS

and NEXT on the data stack. The PUSHD instruction uses one of the following

addressing modes:

•

In the pointer direct addressing mode, the PUSHD [pointer-register]

instruction pushes the two bytes from the specified pointer-register into

TOS and NEXT. The pointer-register expression must be in the range 0

to 3.

•

In the immediate addressing mode, the PUSHD #expression instruction

pushes the 16-bit value of expression into TOS and NEXT.

•

In the immediate addressing mode, the PUSHD #msb,#lsb instruction

pushes an 8-bit most-significant byte (msb) value into NEXT and an 8-bit

least-significant byte (lsb) value into TOS. msb and lsb must each resolve

at link time to a value in the range 0 to 255. This instruction is

equivalent to the PUSHD #expression instruction.

Because the data stack grows towards higher addresses, NEXT holds the most-

significant byte (MSB) and TOS holds the least-significant byte (LSB) of the 16-

bit value that is pushed onto the stack.

The PUSHD instruction applies to Series 3100, 5000, and 6000 devices.

Syntax:

The PUSHD instruction requires one or two operands to specify the location from

which to push the data:

PUSHD [0]

PUSHD [1]

PUSHD [2]

PUSHD [3]

PUSHD #expression

PUSHD #msb,#lsb

The number sign or hash (#) is required to specify the immediate value for the

PUSHD #expression and PUSHD #msb,#lsb instructions.

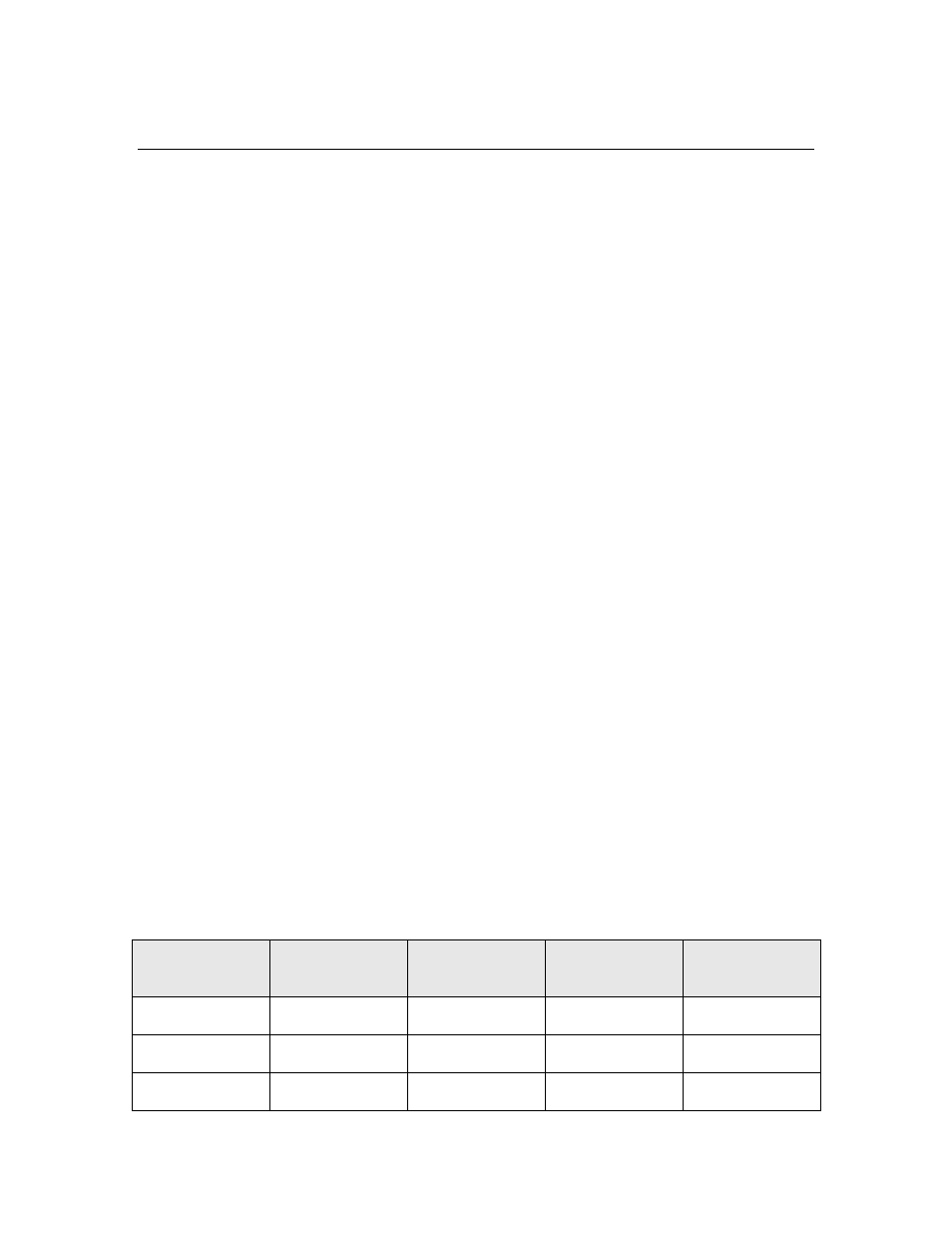

Table 42 describes the attributes of the PUSHD instruction.

Table 42. PUSHD Instruction

Instruction

Hexadecimal

Opcode

Instruction

Size (Bytes)

CPU Cycles

Required

Affect on

Carry Flag

PUSHD [0]

B0

1

6

None

PUSHD [1]

B1

1

6

None

PUSHD [2]

B2

1

6

None

Neuron Assembly Language Reference

107