Echelon Neuron User Manual

Page 118

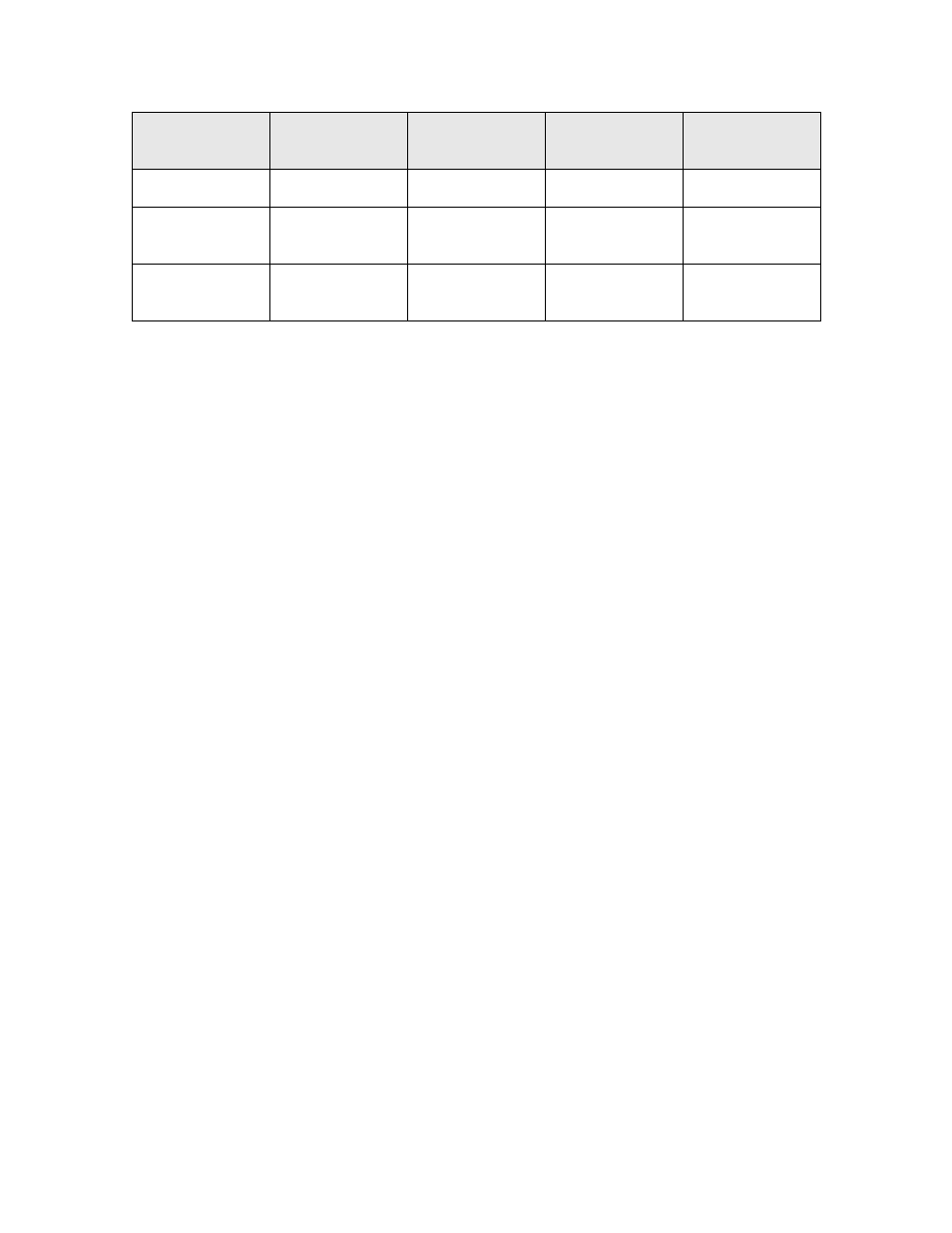

Instruction

Hexadecimal

Opcode

Instruction

Size (Bytes)

CPU Cycles

Required

Affect on

Carry Flag

PUSHD [3]

B3

1

6

None

PUSHD

#expression

B5

3

6

None

PUSHD

#msb,#lsb

B5

3

6

None

Example:

The following example preserves the P1 and P2 pointer registers by pushing

them onto the stack before performing operations that could affect these

registers, then popping them from the stack.

P1 EQU 1

P2 EQU 2

; Preserve P1, P2.

pushd [P1]

pushd [P2]

...

popd [P1]

popd [P2]

ret ; return to caller

108

Neuron Assembly Language Instruction Statements