Xor (exclusive or) – Echelon Neuron User Manual

Page 138

XOR (Exclusive Or)

The XOR instruction performs a logical exclusive OR (XOR) for two numbers.

The OR instruction uses one of two addressing modes:

•

In implicit addressing mode, the XOR instruction retrieves both TOS and

NEXT from the data stack and performs a bitwise logical XOR for them.

TOS and NEXT are consumed, and the result is placed in TOS. The

operation clears the Carry flag.

•

In immediate addressing mode, the XOR instruction performs a bitwise

logical XOR for a specified one-byte constant number with the value of

TOS, and the result is placed in TOS. The value of number must resolve

at link time to a value in the range -128 to +127. The operation clears the

Carry flag.

The XOR instruction applies to Series 3100, 5000, and 6000 devices.

Syntax:

In implicit addressing mode, the XOR instruction requires no operands:

XOR

In immediate addressing mode, the XOR instruction requires one operand:

XOR #number

The number sign or hash (#) is required to specify the immediate value.

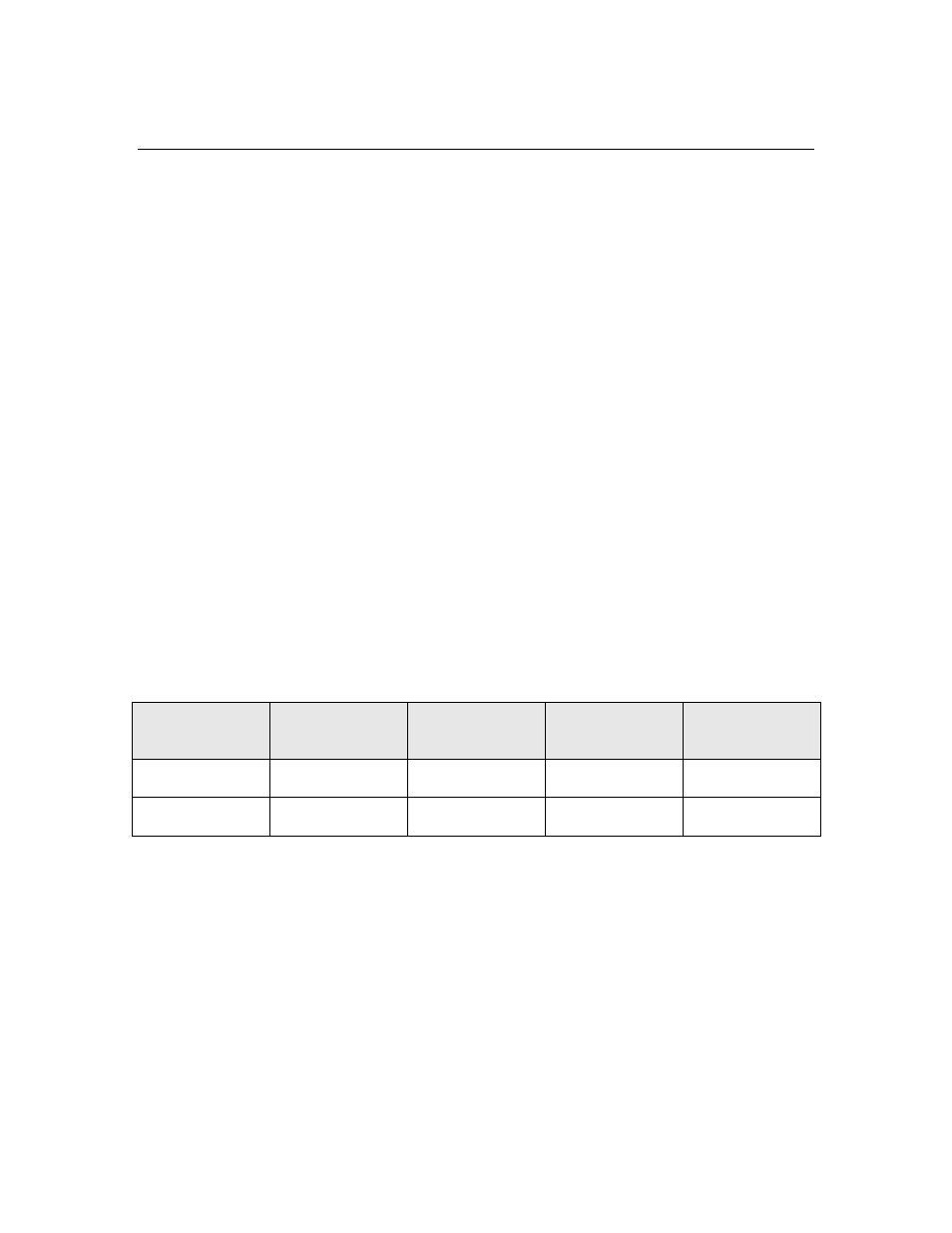

Table 58 describes the attributes of the XOR instruction.

Table 58. XOR Instruction

Instruction

Hexadecimal

Opcode

Instruction

Size (Bytes)

CPU Cycles

Required

Affect on

Carry Flag

XOR

53

1

4

Cleared

XOR #number

5B

2

3

Cleared

Example:

The following example performs the operation (2 XOR 3) XOR 4.

pushs #2 ; (2, -, -)

pushs #3 ; (3, 2, -)

xor ; (1, -, -)

xor #4 ; (5, -, -)

The value of TOS after the first XOR instruction is 1 because 2 XOR 3 = 1. The

XOR #4 instruction performs a logical XOR of 4 with TOS (4 XOR 1), so that TOS

then contains 5.

128

Neuron Assembly Language Instruction Statements