Figure 18 on, For app, E1) applications – Cirrus Logic CS61884 User Manual

Page 52

CS61884

52

DS485F3

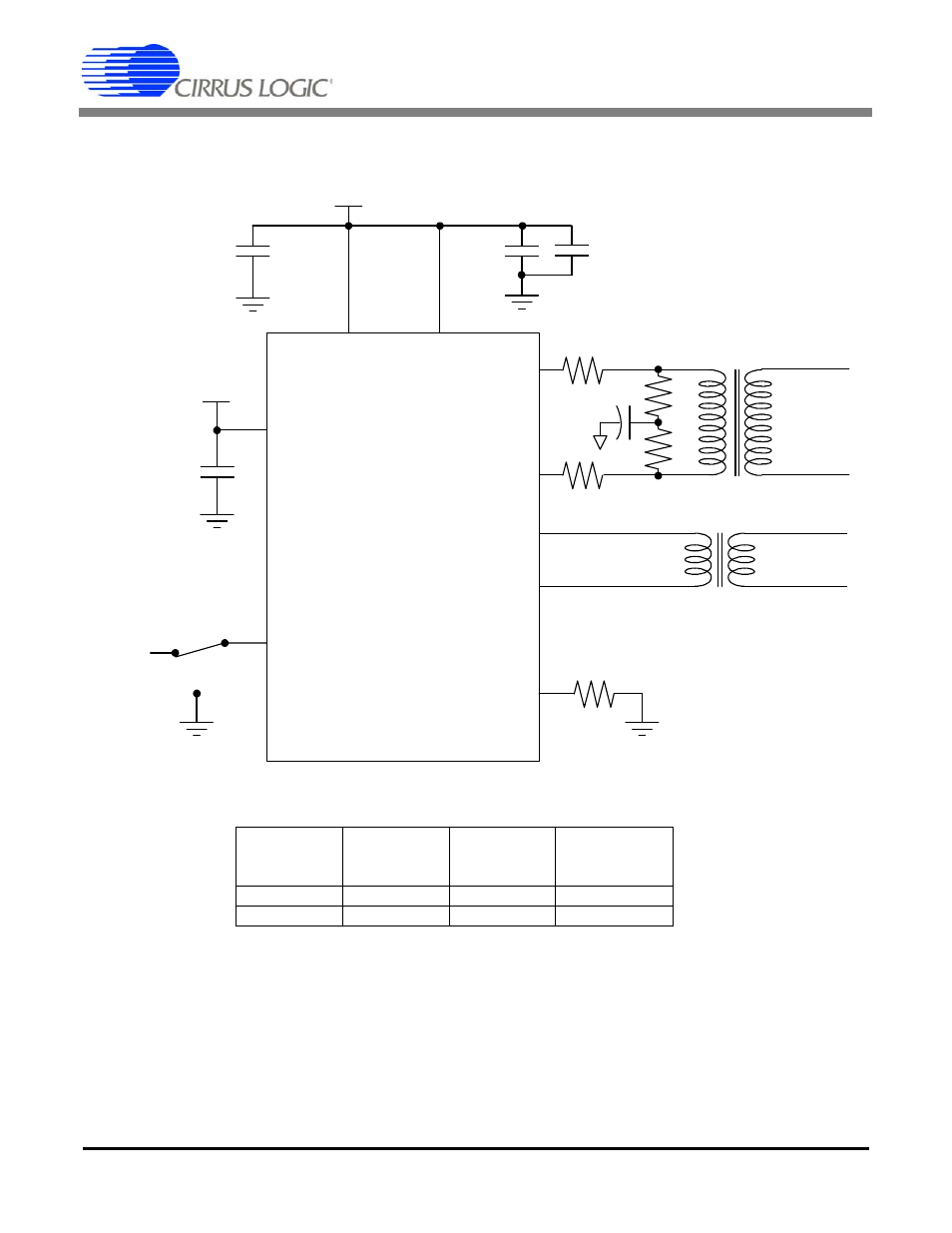

Figure 18. Internal TX, External RX Impedance Matching

+

RGND

0.1

μ F

+3.3V

RV+

T1 1:2

REF

T R I N G

T T I P

T2 1:2

R T I P

R R I N G

R1

R2

13.3k

Ω

GND

CBLSEL

TV+

VCCIO

+3.3V

+

TGND

+

0.1

μ F

GNDIO

NC

100

Ω

75

Ω

Cable

120

Ω

Cable

GND

1k

Ω

1k

Ω

TRANSMIT

LINE

RECEIVE

LINE

0.1

μ F

0.1

μ F

Note 1

Note 1

Note 2

68

μ F

CS61884

One Channel

Notes:

1)Required Capacitor between each TV+, RV+, VCCIO and TGND, RGND, GNDIO

respectively.

2)Common decoupling capacitor for all TVCC and TGND pins.

Component

T1/J1 100

Ω

Twisted Pair

Cable

E1 75

Ω

Coaxial

Cable

E1 120

Ω

Twisted Pair

Cable

R1 (

Ω)

12.5

9.31

15

R2 (

Ω)

12.5

9.31

15

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)