2 control, Table 1. operation mode selection – Cirrus Logic CS61884 User Manual

Page 10

CS61884

10

DS485F3

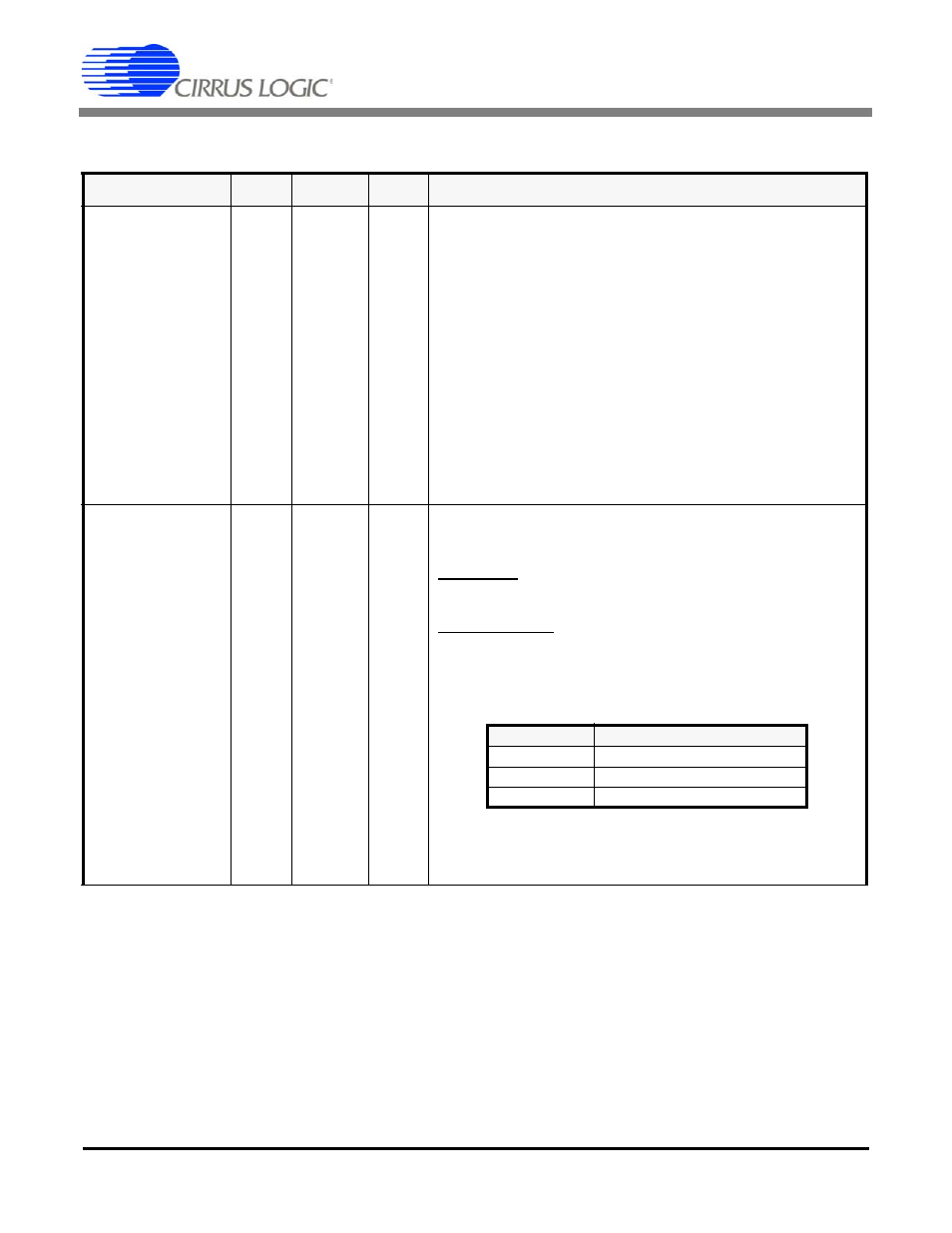

3.2 Control

SYMBOL

LQFP

LFBGA

TYPE

DESCRIPTION

MCLK

10

E1

I

Master Clock Input

This pin is a free running reference clock that should be

either 1.544 MHz for T1/J1 or 2.048 MHz for E1 operation.

This timing reference is used as follows:

- Timing reference for the clock recovery and jitter attenua-

tion circuitry.

- RCLK reference during Loss of Signal (LOS) conditions

- Transmit clock reference during Transmit all Ones (TAOS)

condition

- Wait state timing for microprocessor interface

- When this pin is held “High”, the PLL clock recovery cir-

cuit is disabled. In this mode, the CS61884 receivers

function as simple data slicers.

- When this pin is held “Low”, the receiver paths are pow-

ered down and the output pins RCLK, RPOS, and RNEG

are High-Z.

MODE

11

E2

I

Mode Select

This pin is used to select whether the CS61884 operates in

Serial host, Parallel host or Hardware mode.

Host Mode - The CS61884 is controlled through either a

serial or a parallel microprocessor interface (Refer to

Hardware Mode - The microprocessor interface is disabled

and the device control/status are provided through the pins

on the device.

NOTE: For serial host mode connect this pin to a resistor

divider consisting of two 10K

Ω resistors between

VCCIO and GNDIO.

Table 1. Operation Mode Selection

Pin State

OPERATING Mode

LOW

Hardware Mode

HIGH

Parallel Host Mode

VCCIO/2

Serial Host Mode