Cirrus Logic CS61884 User Manual

Page 50

CS61884

50

DS485F3

73

TCLK3

I

TCLK3

74

LOS2

O

LOS2

75

RNEG2

O

RNEG2

76

RPOS2

O

RPOS2

77

RCLK2

O

RCLK2

78

-

Note 2

HIZ2_B

79

TNEG2

I

TNEG2

80

TPOS2

I

TPOS2

81

TCLK2

I

TCLK2

82

INT_B

O

INT_B

83

RDY

O

RDYOUT

84

-

Note 3

RDYOEN

85

WR_B

I

WR_B

86

RD_B

I

RD_B

87

ALE

I

ALE

88

CS_B

I

CS_B

89

CS_B

I

CS_B_TRI

90

INTL

I

INTL

91

CBLSEL

I

CBLSEL_TRI

92

CBLSEL

I

CBLSEL_IN

93

TCLK5

I

TCLK5

94

TPOS5

I

TPOS5

95

TNEG5

I

TNEG5

96

RCLK5

O

RCLK5

97

RPOS5

O

RPOS5

98

RNEG5

O

RNEG5

99

-

Note 2

HIZ5_B

100

LOS5

O

LOS5

101

TCLK4

I

TCLK4

102

TPOS4

I

TPOS4

103

TNEG4

I

TNEG4

104

RCLK4

O

RCLK4

105

RPOS4

O

RPOS4

106

RNEG4

O

RNEG4

107

-

Note 2

HIZ4_B

108

LOS4

O

LOS4

109

TXOE

I

TXOE

110

CLKE

I

CLKE

Notes:

1)

LPOEN controls the LOOP[7:0] pins. Setting LPOEN to “1” configures LOOP[7:0] as outputs. The output value driven

on the pins are determined by the values written to LPO[7:0]. Setting LPOEN to “0” High-Z all the pins. In this mode,

the input values driven to these LOOP[7:0] can be read via LPI[7:0].

2)

HIZ_B controls the RPOSx, RNEGx, and RCLKx pins. When HIZ_B is High, the outputs are enabled; when HIZ_B is

Low, the outputs are placed in a high impedance state (High-Z).

3)

RDYOEN controls the ACK_B pin. Setting RDYOEN to “1” enables output on ACK_B. Setting ACKEN to “0” High -

Z the ACK_B pin.

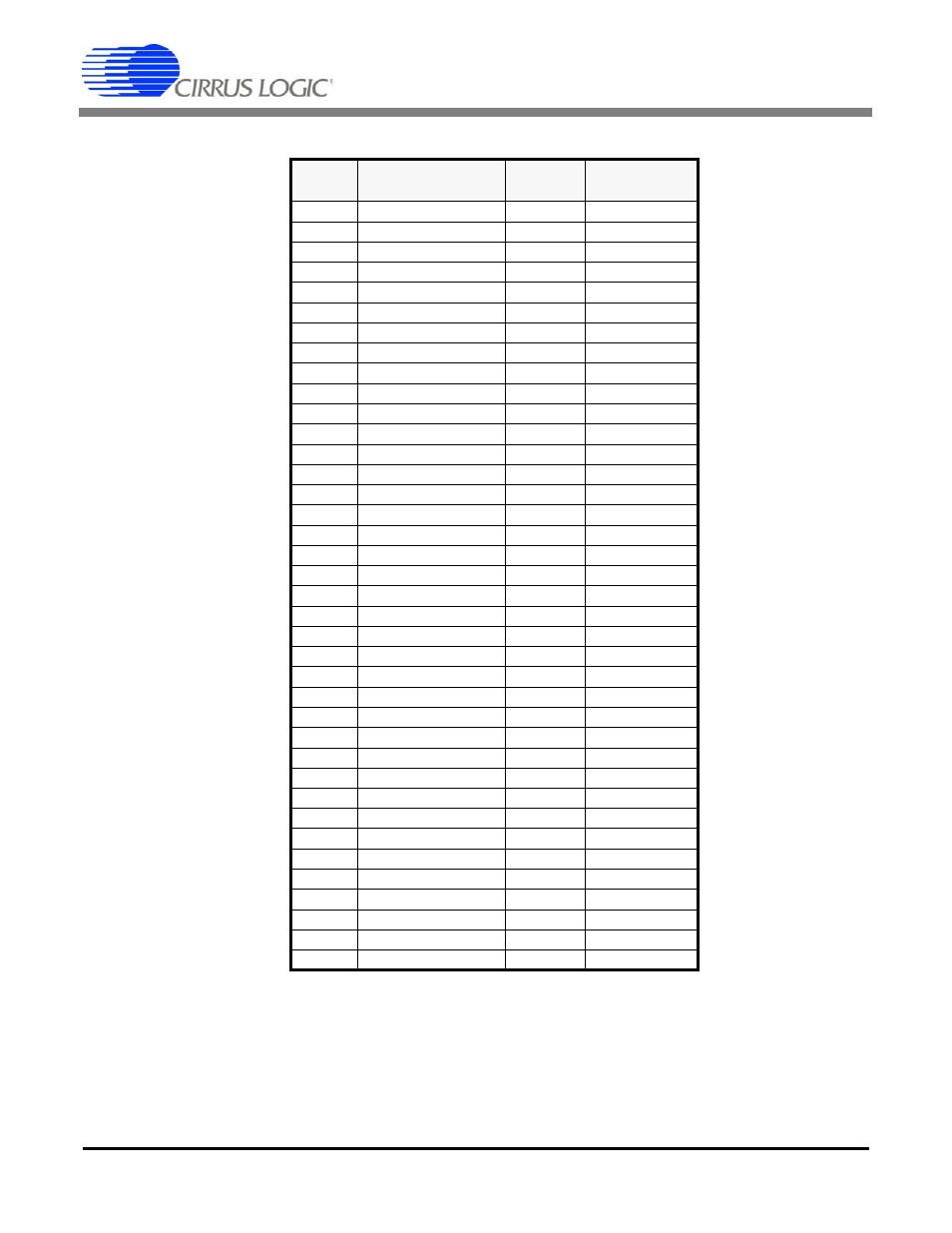

Table 11. Boundary Scan Register (Continued)

BSR

Bit

Pin

Name

Cell

Type

Bit

Symbol