6 alarm indication signal (ais), Jitter attenuator, Table 6. jitter attenuator configurations – Cirrus Logic CS61884 User Manual

Page 28

CS61884

28

DS485F3

During host mode operation, LOS is reported in the

LOS Status Monitor Register. Both the LOS pins

and the register bits reflect LOS status in host mode

operation. The LOS pins and status bits are set high

(indicating loss of signal) during reset, power-up,

or channel powered-down.

10.6 Alarm Indication Signal (AIS)

The CS61884 detects all ones alarm condition per

the relevant ANSI, ITU, and ETSI specifications.

In general, AIS is indicated when the one’s density

of the receive signal exceeds that dictated by the

relevant specification. This feature is only avail-

able in host mode (Refer to

ANSI T1.231 AIS (T1/J1 Mode) - The AIS condi-

tion is declared when less than 9 zeros are received

within a sliding window of 8192 bits. This corre-

sponds to a ones density of 99.9% over a period of

5.3 ms. The AIS condition is cleared when nine or

more zeros are detected in a sliding window of

8192 bits.

ITU G.775 AIS (E1 Mode) - The AIS condition is

declared when less than 3 zeros are received within

two consecutive 512 bit windows. The AIS condi-

tion is cleared when 3 or more zeros are received in

two consecutive 512 bit windows.

ETSI 300 233 (E1 Mode) - The AIS condition is

declared when less than 3 zeros are received in a

512 bit window. The AIS condition is cleared when

a 512 bit window is received containing 3 or more

zeros.

11. JITTER ATTENUATOR

The CS61884 internal jitter attenuators can be

switched into either the receive or transmit paths.

Alternatively, it can be removed from both paths to

reduce the propagation delay.

During Hardware mode operation, the location of

the jitter attenuator for all eight channels are con-

trolled by the JASEL pin (Refer to

configurations). The jitter attenuator’s FIFO length

and corner frequency, can not be changed in hard-

ware mode. The FIFO length and corner frequency

are set to 32 bits and 1.25Hz for the E1 operational

modes and to 32 bits and 3.78Hz in the T1/J1 oper-

ational modes.

During host mode operation, the location of the jit-

ter attenuator for all eight channels are set by bits 0

and 1 in the

Section 14.16 on page 38). The GLOBAL CON-

TROL REGISTER (0Fh) also configures the jitter

attenuator’s FIFO length (bit 3) and corner fre-

quency (bit 2).

The attenuator consists of a 64-bit FIFO, a narrow-

band monolithic PLL, and control logic. The jitter

attenuator requires no external crystal. Signal jitter

is absorbed in the FIFO which is designed to nei-

ther overflow nor underflow.

If overflow or underflow is imminent, the jitter

transfer function is altered to ensure that no bit-er-

rors occur. A configuration option is provided to

reduce the jitter attenuator FIFO length from 64

bits to 32 bits in order to reduce propagation delay.

The jitter attenuator -3 dB knee frequency depends

on the settings of the Jitter Attenuator FIFO length

and the Jitter Attenuator Corner Frequency bits 2

and 3, in the

Section 14.16 on page 38)). Setting the lowest cor-

ner frequency guarantees jitter attenuation compli-

ance to European specifications TBR 12/13 and

ETSI ETS 300 011 in E1 mode. The jitter attenua-

tor is also compliant with ITU-T G.735, G.742,

G.783 and AT&T Pub. 62411 (Refer to

and

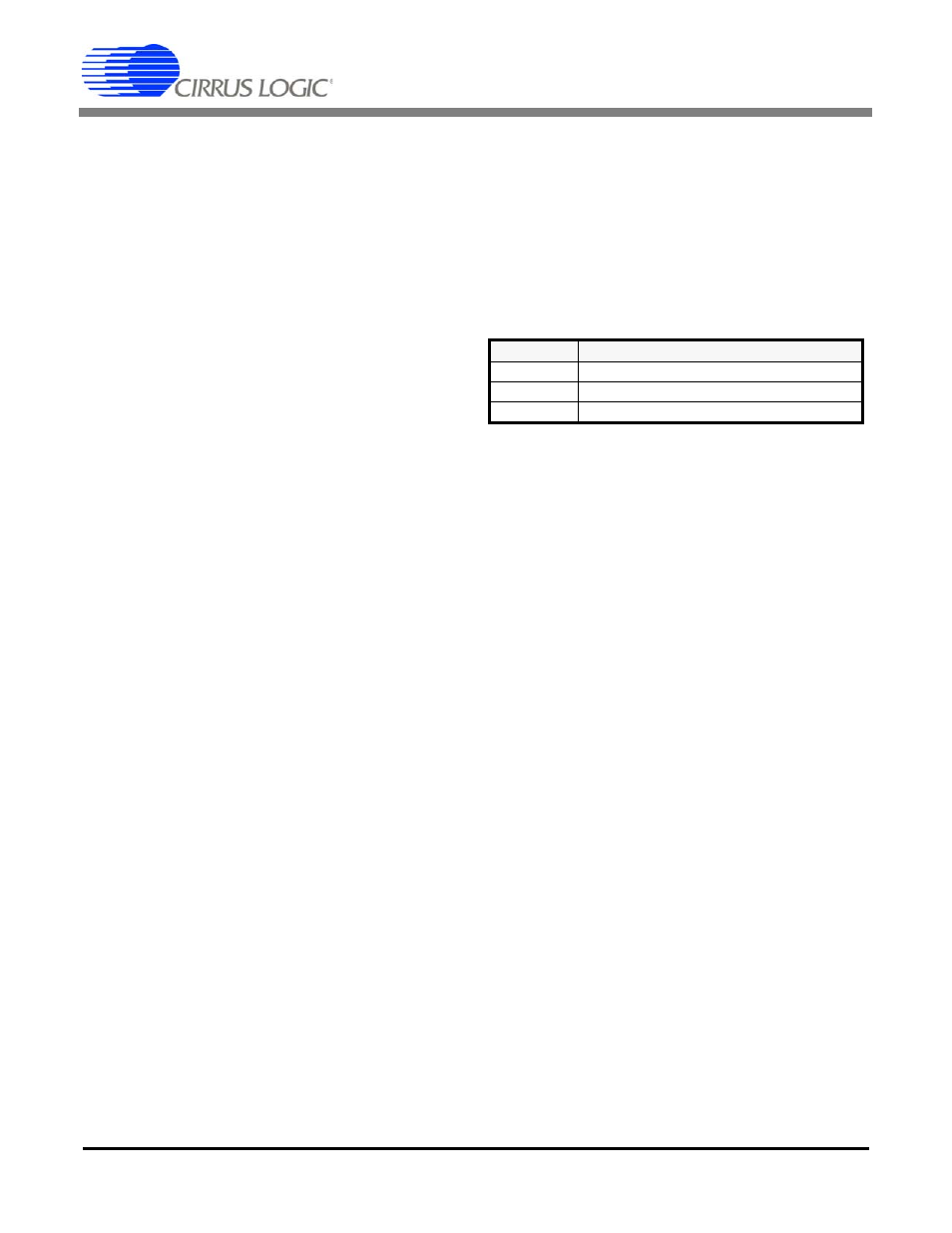

Table 6. Jitter Attenuator Configurations

PIN STATE

JITTER ATTENUATOR POSITON

LOW

Transmit Path

HIGH

Receive Path

OPEN

Disabled