3 digital loopback, 4 remote loopback, 3 digital loopback 12.4 remote loopback – Cirrus Logic CS61884 User Manual

Page 30: In hardware mode, analog, Figure 9 on

CS61884

30

DS485F3

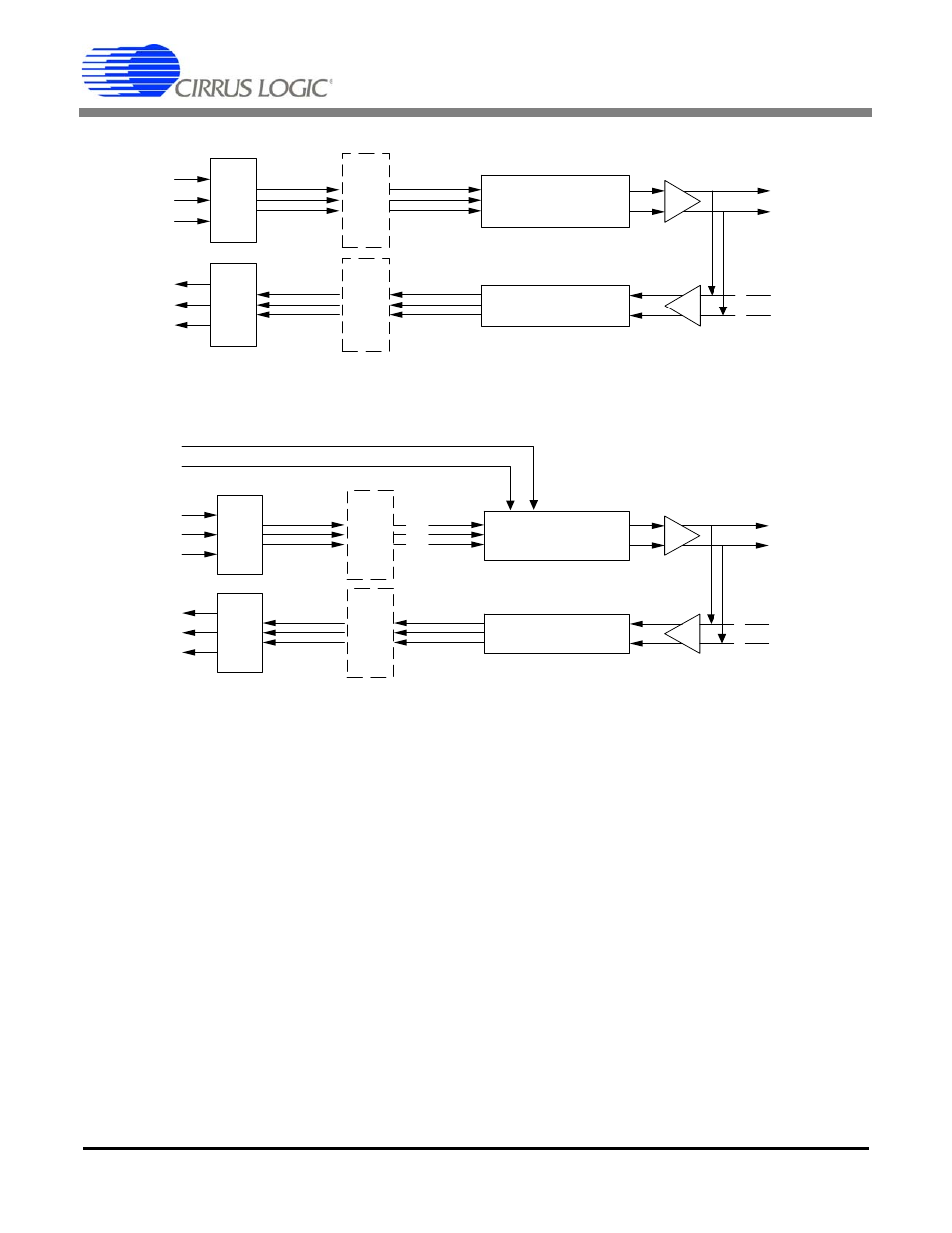

12.3 Digital Loopback

Digital Loopback causes the TCLK, TPOS, and

TNEG (or TDATA) inputs to be looped back

through the jitter attenuator (if enabled) to the

RCLK, RPOS, and RNEG (or RDATA) outputs.

The receive line interface is ignored, but data at

TPOS and TNEG (or TDATA) continues to be

transmitted to the line interface at TTIP and

TRING (Refer to

).

Digital Loopback is only available during host

mode. It is selected using the appropriate bit in the

Digital Loopback Reset Register (0Ch)

NOTE: TAOS can also be used during the Digital Loop-

back operation for the selected channel (Refer

to

).

12.4 Remote Loopback

In remote loopback, the RPOS/RNEG and RCLK

outputs are internally input to the transmit circuits

for output on TTIP/TRING. In this mode the

TCLK, TPOS and TNEG inputs are ignored. (Refer

to

)

.

In hardware mode, Re-

mote Loopback is selected by driving the LOOP

pin for a certain channel low. In host mode, Remote

Loopback is selected for a given channel by writing

a one to the appropriate bit in the

NOTE: In hardware mode, Remote Loopback over-

rides TAOS for the selected channel. In host

mode, TAOS overrides Remote Loopback.

Encoder

Decoder

TTIP

TRING

RTIP

RRING

TNEG

TCLK

RNEG

RCLK

TPOS

RPOS

Clock Recovery &

Data Recovery

Transmit

Control &

Pulse Shaper

Jitter

Attenuator

Jitter

Attenuator

Figure 8. Analog Loopback Block Diagram

Encoder

Decoder

TNEG

TCLK

RNEG

RCLK

TPOS

RPOS

TAOS

MCLK

(All One's)

TTIP

TRING

RTIP

RRING

Clock Recovery &

Data Recovery

Transmit

Control &

Pulse Shaper

Jitter

Attenuator

Jitter

Attenuator

Figure 9. Analog Loopback with TAOS Block Diagram