1 bipolar mode, 2 unipolar mode, 3 rz mode – Cirrus Logic CS61884 User Manual

Page 25: 4 transmitter powerdown / high-z, 5 transmit all ones (taos), Table 5, Table 5, “hardware mode line, This sets the pulse s, E1, when there is no mclk present (refer to, Mode

CS61884

DS485F3

25

The CS61884 also allows the user to customize the

transmit pulse shapes to compensate for non-stan-

dard cables, transformers, or protection circuitry.

For further information on the AWG Refer to

For more information on the host mode registers,

refer to

9.1 Bipolar Mode

Bipolar mode provides transparent operation for

applications in which the line coding function is

performed by an external framing device. In this

mode, the falling edge of TCLK samples NRZ data

on TPOS/TNEG for transmission on TTIP/TRING.

9.2 Unipolar Mode

In unipolar mode, the CS61884 is configured such

that transmit data is encoded using B8ZS, HDB3,

or AMI line codes. This mode is activated by hold-

ing TNEG/UBS “High” for more than 16 TCLK

cycles. Transmit data is input to the part via the

TPOS/TDATA pin on the falling edge of TCLK.

When operating the part in hardware mode, the

CODEN pin is used to select between B8ZS/HDB3

or AMI encoding. During host mode operation, the

line coding is selected via the

(See Section 14.16 on page 38).

NOTE: The encoders/decoders are selected for all

eight channels in both hardware and host

mode.

9.3 RZ Mode

In RZ mode, the internal pulse shape circuitry is

bypassed and RZ data driven into TPOS/TNEG is

transmitted on TTIP/TRING. In this mode, the

pulse width of the transmitter output is determined

by the width of the RZ signal input to

TPOS/TNEG. This mode is entered when MCLK

does not exist and TCLK is held “High” for at least

12

μsec.

9.4 Transmitter Powerdown / High-Z

The transmitters can be forced into a high imped-

ance, low power state by holding TCLK of the ap-

propriate channel low for at least 12

μs or 140

MCLK cycles. In hardware and host mode, the

TXOE pin forces all eight transmitters into a high

impedance state within 1

μs.

In host mode, each transmitter is individually con-

trollable using the

(See Section 14.19 on page 39). The TXOE pin can

be used in host mode, but does not effect the con-

tents of the Output Enable Register. This feature is

useful in applications that require redundancy.

9.5 Transmit All Ones (TAOS)

When TAOS is activated, continuous ones are

transmitted on TTIP/TRING using MCLK as the

transmit timing reference. In this mode, the TPOS

and TNEG inputs are ignored.

In hardware mode, TAOS is activated by pulling

TCLK “High” for more than 16 MCLK cycles.

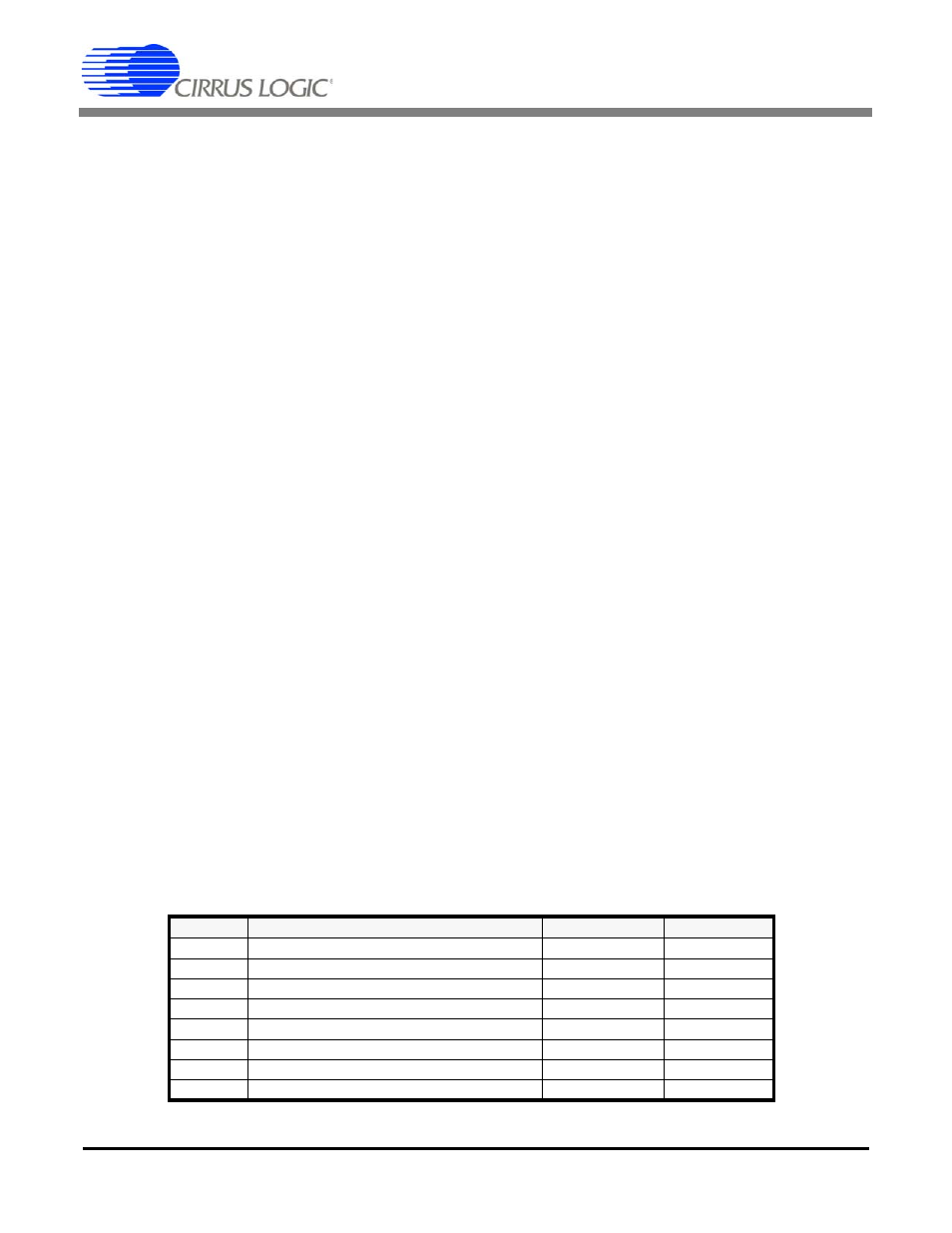

Table 5. Hardware Mode Line Length Configuration Selection

LEN[2:0]

Transmit Pulse Configuration

Line Z

Operation

000

E1 3.0V / E1 2.37V

120

Ω / 75Ω

E1

001

DS1, Option A (undershoot)

100

Ω

T1/J1

010

DS1, Option A (0 dB)

100

Ω

T1/J1

011

DSX-1: 0-133 ft. (0.6dB)

100

Ω

T1/J1

100

DSX-1: 133-266 ft. (1.2dB)

100

Ω

T1/J1

101

DSX-1: 266-399 ft. (1.8dB)

100

Ω

T1/J1

110

DSX-1: 399-533 ft. (2.4dB)

100

Ω

T1/J1

111

DSX-1: 533-655 ft. (3.0dB)

100

Ω

T1/J1