7 los interrupt enable register (06h), 8 dfm interrupt enable register (07h), 9 los interrupt status register (08h) – Cirrus Logic CS61884 User Manual

Page 36: 10 dfm interrupt status register (09h), 11 software reset register (0ah), 12 performance monitor register (0bh), Monitoring via the, Performance monitor regis, Ter (0bh), Dfm interrupt enable register (07h)

CS61884

36

DS485F3

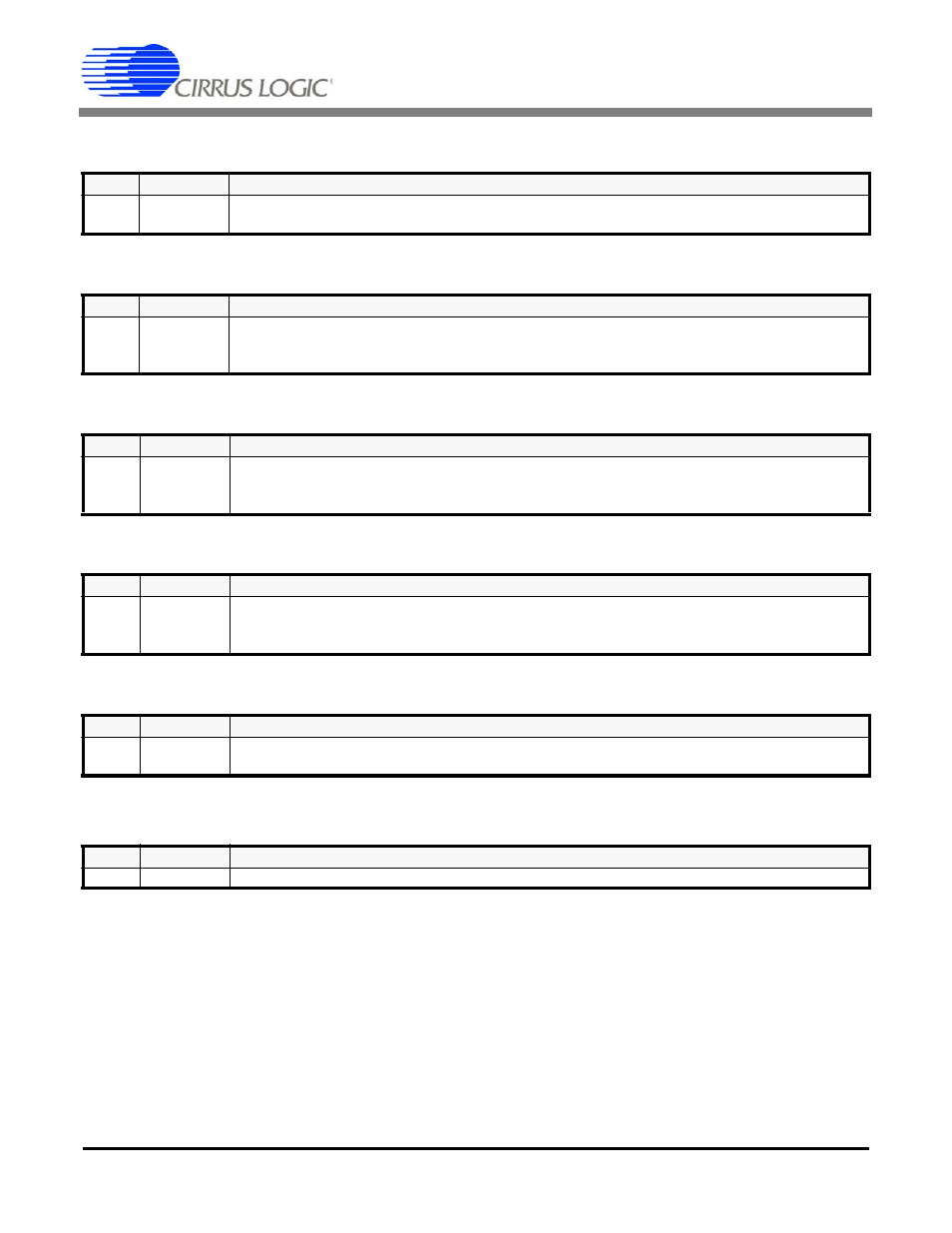

14.7 LOS Interrupt Enable Register (06h)

14.8 DFM Interrupt Enable Register (07h)

14.9

LOS Interrupt Status Register (08h)

14.10

DFM Interrupt Status Register (09h)

14.11 Software Reset Register (0Ah)

14.12 Performance Monitor Register (0Bh)

BIT

NAME

Description

[7:0]

LOSE 7-0 Any change in a LOS Status Register bits will cause the INT pin to go low if corresponding bit

in this register is set to “1”. Register bits default to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

DFME 7-0

Enables interrupts for failures detected by the DFM. Any change in a DFM Status Register bit

will cause an interrupt if the corresponding bit is set to “1” in this register. Register bits

default to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

LOSI 7-0

Bit n of this register is set to “1” to indicate a status change in bit n of the LOS Status Regis-

ter. The bits in this register indicate a change in status since the last cleared LOS interrupt.

Register bits default to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

DFMI 7-0

Bit n of this register is set to “1” to indicate a status change in bit n of the DFM Status Regis-

ter. The bits in this register indicate a change in status since the last cleared DFM interrupt.

Register bits default to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

SRES 7-0 Writing to this register initializes all registers to their default settings. Register bits default to

00h after power-up or reset.

BIT

NAME

Description

[7:4]

RSVD 7-4

RESERVED (These bits must be set to 0.)