3 parallel port operation, Figure 13. serial read/write format (spol = 0), Figure 13 – Cirrus Logic CS61884 User Manual

Page 33: Illustrates the

CS61884

DS485F3

33

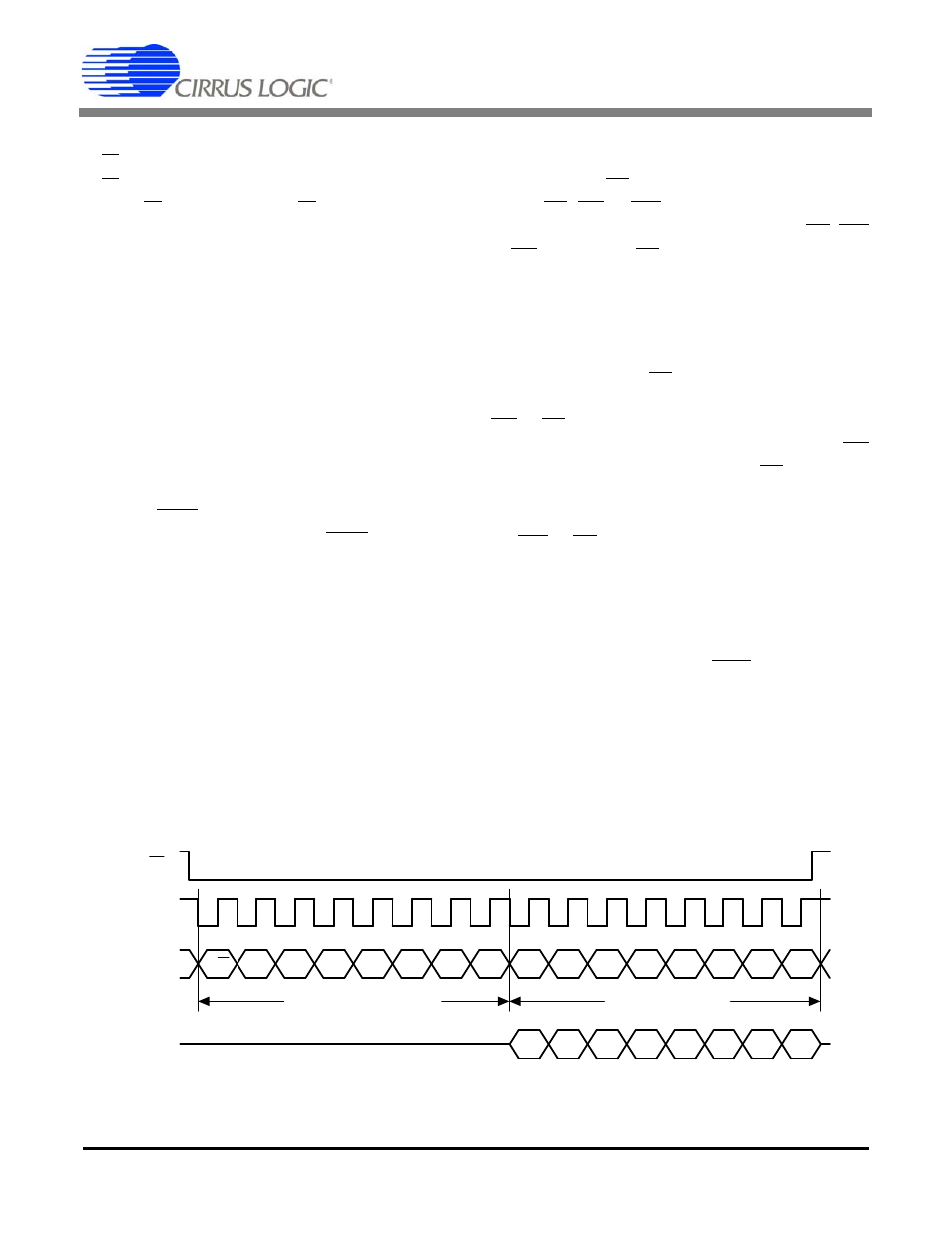

As illustrated in

, the ACB consists of a

R/W bit, address field, and two reserved bits. The

R/W bit specifies if the current register access is a

read (R/W = 1) or a write (R/W = 0) operation. The

address field specifies the register address from

0x00 to 0x1f.

13.3 Parallel Port Operation

Parallel port host mode operation is selected when

the MODE pin is high. In this mode, the CS61884

register set is accessed using an 8-bit, multiplexed

bidirectional address/data bus D[7:0]. Timing over

the parallel port is independent of the transmit and

receive system timing.

The device is compatible with both Intel and Mo-

torola bus formats. The Intel bus format is selected

when the MOT/INTL pin is high and the Motorola

bus format is selected when the MOT/INTL pin is

low. In either mode, the interface can have the ad-

dress and data multiplexed over the same 8-bit bus

or on separate busses. This operation is controlled

with the MUX pin; MUX = 1 means that the paral-

lel port has its address and data multiplexed over

the same bus; MUX = 0 defines a non-multiplexed

bus. The timing for the different modes are shown

in

,

,

,

and

Non-multiplexed Intel and Motorola modes are

shown in

,

and

. The CS pin initiates the cycle, followed

by the DS, RD or WR pin. Data is latched into or

out of the part using the rising edge of the DS, WR

or RD pin. Raising CS ends the cycle.

Multiplexed Intel and Motorola modes are shown

in

. A

read or write is initiated by writing an address byte

to D[7:0]. The device latches the address on the

falling edge of ALE(AS). During a read cycle, the

register data is output during the later portion of the

RD or DS pulses. The read cycle is terminated and

the bus returns to a high impedance state as RD

transitions high in Intel timing or DS transitions

high in Motorola timing. During a write cycle, val-

id write data must be present and held stable during

the WR or DS pulses.

In Intel mode, the RDY output pin is normally in a

high impedance state; it pulses low once to ac-

knowledge that the chip has been selected, and high

again to acknowledge that data has been written or

read. In Motorola mode, the ACK pin performs a

similar function; it drives high to indicate that the

address has been received by the part, and goes low

again to indicate that data has been written or read.

CS

SDI

SCLK

SDO

CLKE=0

0

R/W

0

0

0

0

0

1

D0

D1

D2

D5

D3

D6

D4

D7

D0

D1

D2

D5

D3

D6

D4

D7

Address/Command Byte

Data Input/Output

Figure 13. Serial Read/Write Format (SPOL = 0)