16 global control register (0fh), 17 line length channel id register (10h), Line length – Cirrus Logic CS61884 User Manual

Page 38: Channel id register (10h), See section 14.17 on, Line length channel id, Register (10h), Global control register (0fh), And 1 in the

CS61884

38

DS485F3

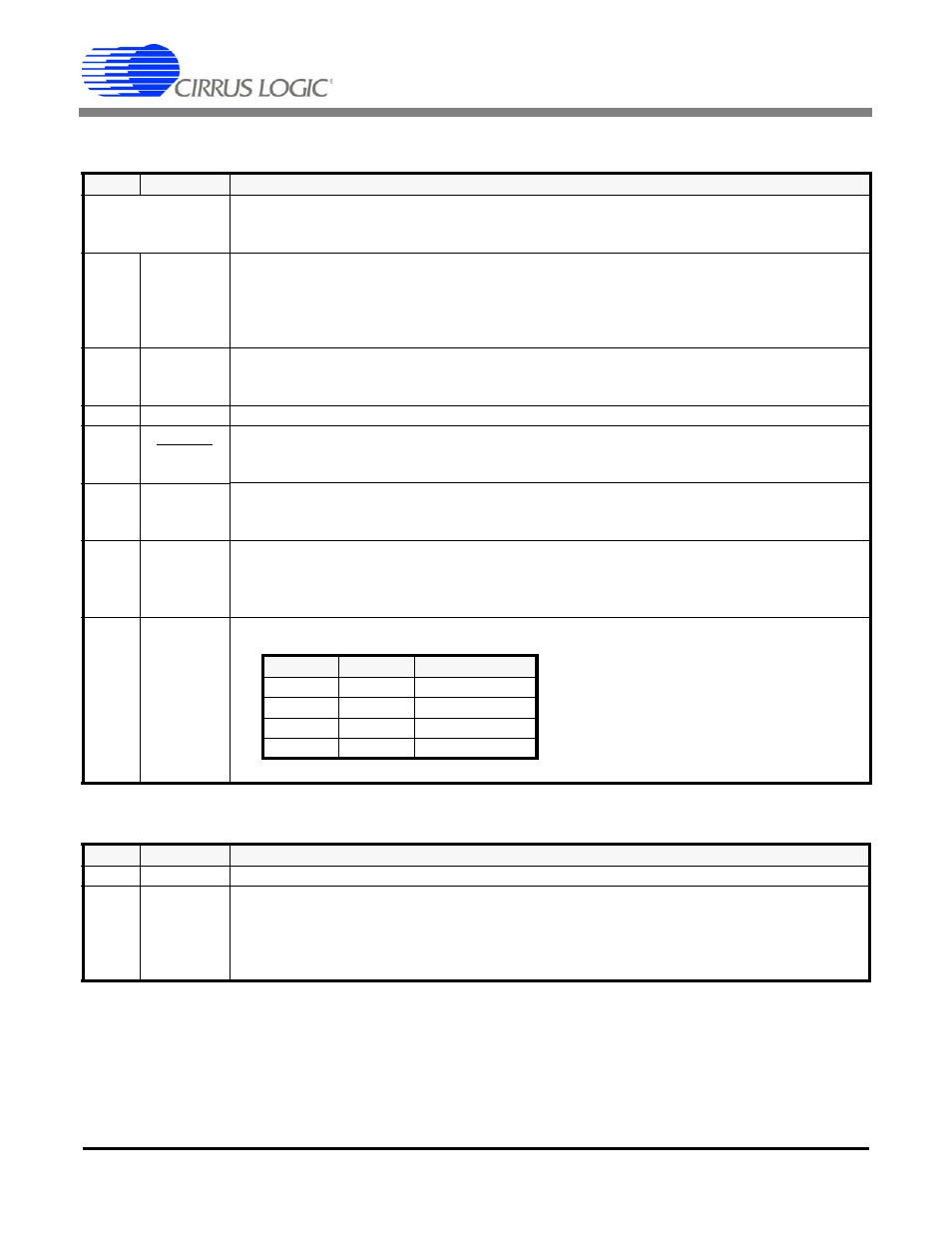

14.16 Global Control Register (0Fh)

14.17 Line Length Channel ID Register (10h)

BIT

NAME

Description

This register is the global control for the AWG Auto-Increment, Automatic AIS insertion,

encoding/decoding and the jitter attenuators location, FIFO length and corner frequency for

all eight channels. Register bits default to 00h after power-up or reset.

[7]

AWG Auto-

Increment

The AWG Auto-Increment bit indicates whether to auto-increment the

(See Section 14.24 on page 40) after each access. Thus, when this bit is set,

the phase samples address portion of the address register increments after each read or

write access. This bit must be set before any bit in the AWG Enable register is set, if this

function is required.

[6]

RAISEN

On LOS, this bit controls the automatic AIS insertion into all eight receiver paths.

0 = Disabled

1 = Enabled

[5]

RSVD

RESERVED (This bit must be set to 0.)

[4]

CODEN

Line encoding/decoding Selection

0 = B8ZS/HDB3 (T1/J1/E1 respectively)

1 = AMI

[3]

FIFO

LENGTH

Jitter Attenuator FIFO length Selection

0 = 32 bits

1 = 64 bits

[2]

JACF

Jitter Attenuator Corner Frequency Selection

E1 T1/J1

0 = 1.25Hz 3.78Hz

1 = 2.50Hz 7.56Hz

[1:0]

JASEL [1:0]

These bits select the position of the Jitter Attenuator.

BIT

NAME

Description

[7:3]

RSVD 7-3

RESERVED (These bits must be set to 0.)

[2:0]

LLID 2-0

The value written to these bits specify the LIU channel for which the Pulse Shape Configura-

tion Data (register 11h) applies. For example, writing a value of a binary 000 to the 3-LSBs

will select channel 0. The pulse shape configuration data for the channel specified in this reg-

ister are written or read through the Line Length Data Register (11h). Register bits default

to 00h after power-up or reset.

JASEL 1 JASEL 0

POSITION

0

0

Disabled

0

1

Transmit Path

1

0

Disabled

1

1

Receive Path