Cirrus Logic CS61884 User Manual

Page 17

CS61884

DS485F3

17

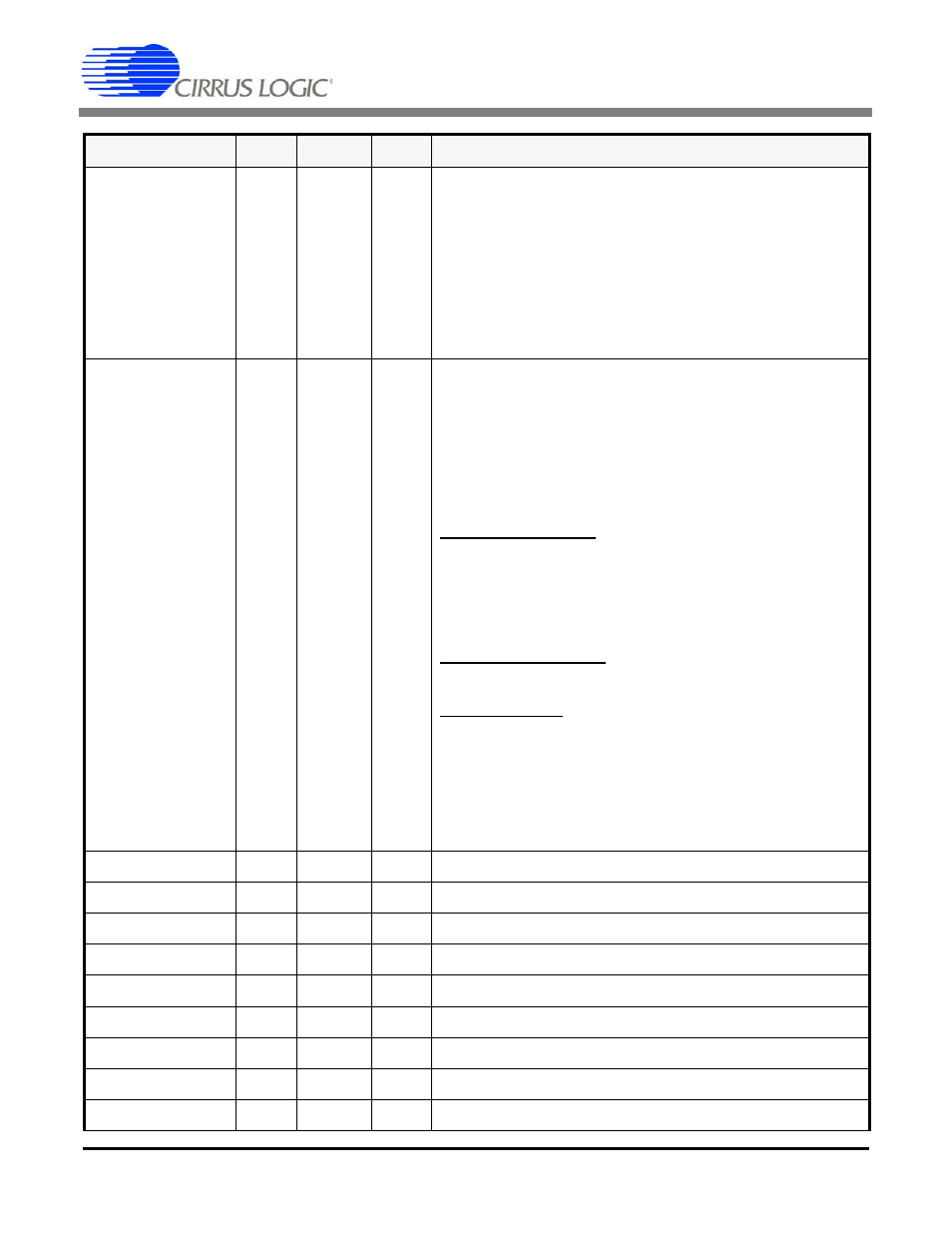

RCLK0

39

P1

O

Receive Clock Output Port 0

- When MCLK is active, this pin outputs the recovered clock

from the signal input on RTIP and RRING. In the event of

LOS, the RCLK output transitions from the recovered clock

to MCLK.

- If MCLK is held “High”, the clock recovery circuitry is dis-

abled and the RCLK output is driven by the XOR of RNEG

and RPOS.

- If MCLK is held “Low”, this output is in a high-impedance

state.

RPOS0/RDATA0

RNEG0/BPV0

40

41

P2

P3

O

O

Receive Positive Pulse/ Receive Data Output Port 0

Receive Negative Pulse/Bipolar Violation Output Port 0

The function of the RPOS/RDATA and RNEG/BPV outputs

are determined by whether Unipolar, Bipolar, or RZ input

mode has been selected. During LOS, the RPOS/RNEG

outputs will remain active.

NOTE: The RPOS/RNEG outputs can be High-Z by holding

MCLK Low.

Bipolar Output Mode - When configured for Bipolar opera-

tion, NRZ Data is recovered from RTIP/RRING and output

on RPOS/RNEG. A high signal on RPOS or RNEG corre-

spond to the receipt of a positive or negative pulse on

RTIP/RRING respectively. The RPOS/RNEG outputs are

valid on the falling or rising edge of RCLK as configured by

CLKE.

Unipolar Output Mode - When unipolar mode is activated,

the recovered data is output on RDATA. The decoder sig-

nals bipolar Violations on the RNEG/BPV pin.

RZ Output Mode - In this mode, the RPOS/RNEG pins

output RZ data recovered by slicing the signal present on

RTIP/RRING. A positive pulse on RTIP with respect to

RRING generates a logic 1 on RPOS; a positive pulse on

RRING with respect to RTIP generates a logic 1 on RNEG.

The polarity of the output on RPOS/RNEG is selectable us-

ing the CLKE pin. In this mode, external circuitry is used to

recover clock from the received signal.

TCLK1

29

L1

I

Transmit Clock Input Port 1

TPOS1/TDATA1

30

L2

I

Transmit Positive Pulse/Transmit Data Input Port 1

TNEG1/UBS1

31

L3

I

Transmit Negative Pulse/Unipolar-Bipolar Select Port 1

RCLK1

32

M1

O

Receive Clock Output Port 1

RPOS1/RDATA1

33

M2

O

Receive Positive Pulse/ Receive Data Output Port 1

RNEG1/BPV1

34

M3

O

Receive Negative Pulse/Bipolar Violation Output Port 1

TCLK2

81

L14

I

Transmit Clock Input Port 2

TPOS2/TDATA2

80

L13

I

Transmit Positive Pulse/Transmit Data Input Port 2

TNEG2/UBS2

79

L12

I

Transmit Negative Pulse/Unipolar-Bipolar Select Port 2

SYMBOL

LQFP

LFBGA

TYPE

DESCRIPTION