Register descriptions, 1 revision/idcode register (00h), 2 analog loopback register (01h) – Cirrus Logic CS61884 User Manual

Page 35: 3 remote loopback register (02h), 4 taos enable register (03h), 5 los status register (04h), 6 dfm status register (05h), Taos, Enable register (03h), See section 14.4 on

CS61884

DS485F3

35

14. REGISTER DESCRIPTIONS

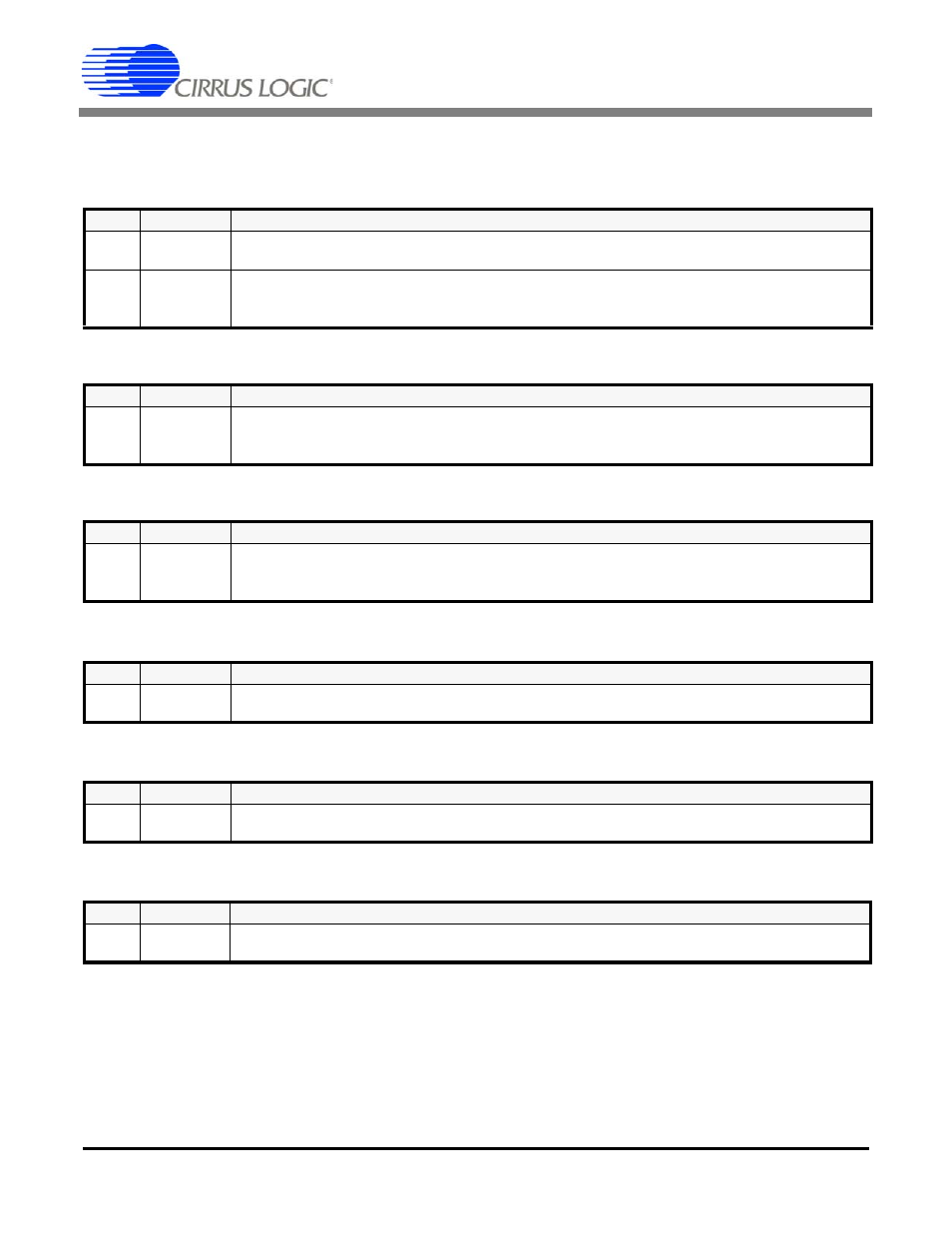

14.1 Revision/IDcode Register (00h)

14.2

Analog Loopback Register (01h)

14.3 Remote Loopback Register (02h)

14.4

TAOS Enable Register (03h)

14.5 LOS Status Register (04h)

14.6

DFM Status Register (05h)

BIT

NAME

Description

[7:4]

REVI 7-4

Bits [7:4] are taken from the least-significant nibble of the Device IDCode, which are 0100.

(Refer to

(See Section 16.3 on page 48).

[3:0]

REVI 3-0

Bits [3:0] are the revision bits from the JTAG IDCODE register, CS61884 Revision A = 0000.

These bits are subject to change with the revision of the device (Refer to

(See Section 16.3 on page 48).

BIT

NAME

Description

[7:0]

ALBK 7-0

Enables analog loopbacks. A “1” in bit n enables the loopback for channel n. Refer to

(See Section 12.2 on page 29) for a complete explanation. Register bits default

to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

RLBK 7-0

Enables remote loopbacks. A “1” in bit n enables the loopback for channel n. Refer to

(See Section 12.4 on page 30) for a complete explanation. Register bits

default to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

TAOE 7-0

A “1” in bit n of this register turns on the TAOS generator in channel n. Register bits default

to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

LOSS 7-0 Register bit n is read as “1” when LOS is detected on channel n. Register bits default to

00h after power-up or reset.

BIT

NAME

Description

[7:0]

DFMS 7-0 Driver Failure Monitor. The DFM will set bit n to “1” when it detects a short circuit in channel

n. Register bits default to 00h after power-up or reset.