Cirrus Logic CS42L51 User Manual

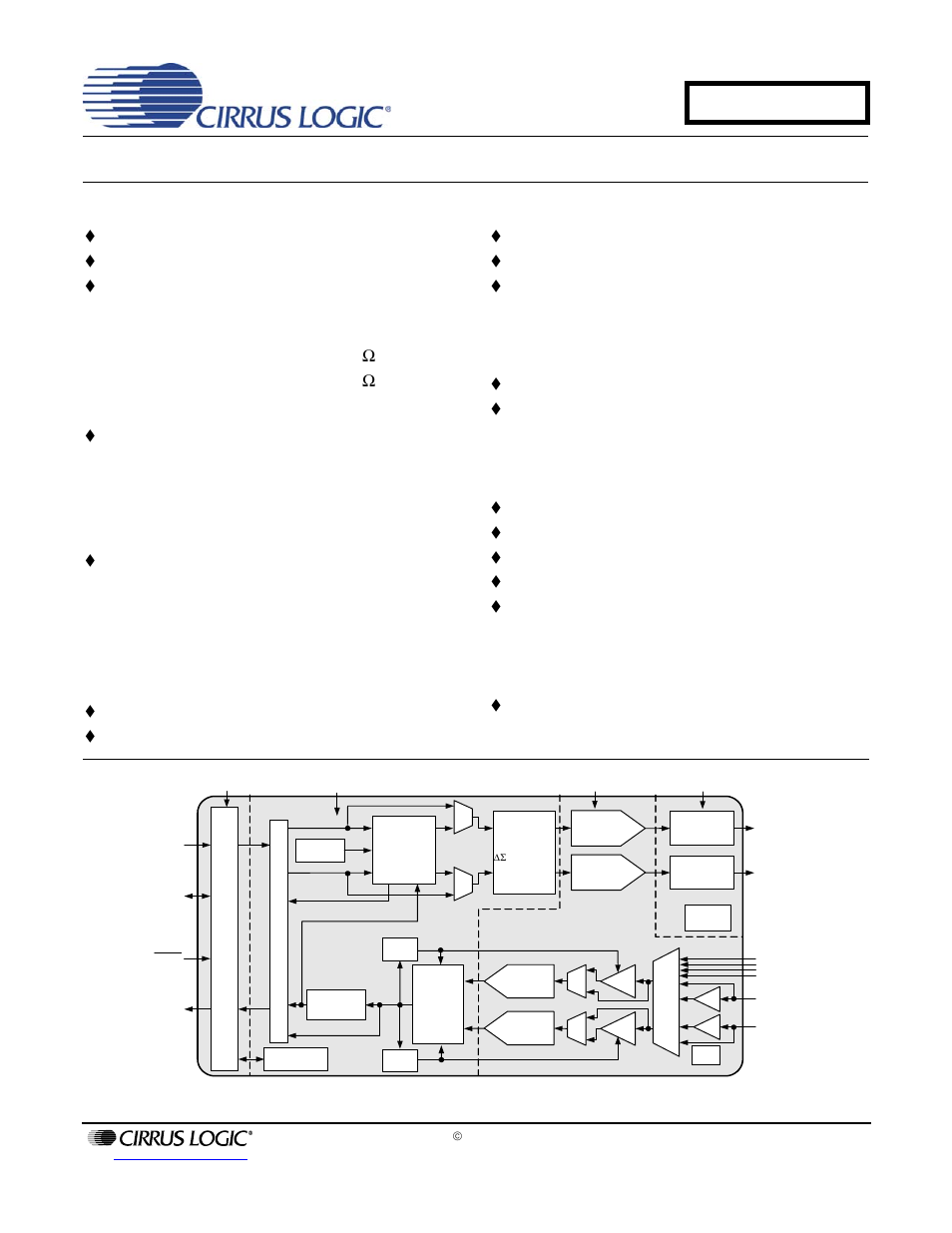

Cs42l51, Low power, stereo codec with headphone amp, Digital to analog features

Table of contents

Document Outline

- 1. Pin Descriptions - Software (Hardware) Mode

- 2. Typical Connection Diagrams

- 3. Characteristic and Specification Tables

- Specified Operating Conditions

- Absolute Maximum Ratings

- Analog Input Characteristics (Commercial - CNZ)

- Analog Input Characteristics (Automotive - DNZ)

- ADC Digital Filter Characteristics

- Analog Output Characteristics (Commercial - CNZ)

- Analog Output Characteristics (Automotive - DNZ)

- Line Output Voltage Characteristics

- Headphone Output Power Characteristics

- Combined DAC Interpolation & on-Chip Analog FIlter Response

- Switching Specifications - Serial Port

- Switching Specifications - I·C® Control Port

- Switching Characteristics - SPI™ Control Port

- DC Electrical Characteristics

- Digital Interface Specifications & Characteristics

- Power Consumption

- 4. Applications

- 4.1 Overview

- 4.2 Hardware Mode

- 4.3 Analog Inputs

- 4.4 Analog Outputs

- 4.5 Serial Port Clocking

- 4.6 Digital Interface Formats

- 4.7 Initialization

- 4.8 Recommended Power-Up Sequence

- 4.9 Recommended Power-Down Sequence

- 4.10 Software Mode

- 5. Register Quick Reference

- 6. Register Description

- 6.1 Chip I.D. and Revision Register (Address 01h) (Read Only)

- 6.2 Power Control 1 (Address 02h)

- 6.3 MIC Power Control & Speed Control (Address 03h)

- 6.4 Interface Control (Address 04h)

- 6.5 MIC Control (Address 05h)

- 6.6 ADC Control (Address 06h)

- 6.7 ADCx Input Select, Invert & Mute (Address 07h)

- 6.8 DAC Output Control (Address 08h)

- 6.9 DAC Control (Address 09h)

- 6.10 ALCX & PGAX Control: ALCA, PGAA (Address 0Ah) & ALCB, PGAB (Address 0Bh)

- 6.11 ADCx Attenuator: ADCA (Address 0Ch) & ADCB (Address 0Dh)

- 6.12 ADCx Mixer Volume Control: ADCA (Address 0Eh) & ADCB (Address 0Fh)

- 6.13 PCMX Mixer Volume Control: PCMA (Address 10h) & PCMB (Address 11h)

- 6.14 Beep Frequency & Timing Configuration (Address 12h)

- 6.15 Beep Off Time & Volume (Address 13h)

- 6.16 Beep Configuration & Tone Configuration (Address 14h)

- 6.17 Tone Control (Address 15h)

- 6.18 AOUTx Volume Control: AOUTA (Address 16h) & AOUTB (Address 17h)

- 6.19 PCM Channel Mixer (Address 18h)

- 6.20 Limiter Threshold SZC Disable (Address 19h)

- 6.21 Limiter Release Rate Register (Address 1Ah)

- 6.22 Limiter Attack Rate Register (Address 1Bh)

- 6.23 ALC Enable & Attack Rate (Address 1Ch)

- 6.24 ALC Release Rate (Address 1Dh)

- 6.25 ALC Threshold (Address 1Eh)

- 6.26 Noise Gate Configuration & Misc. (Address 1Fh)

- 6.27 Status (Address 20h) (Read Only)

- 6.28 Charge Pump Frequency (Address 21h)

- 7. Analog Performance Plots

- 8. Example System Clock Frequencies

- 9. PCB Layout Considerations

- 10. ADC & DAC Digital Filters

- 11. Parameter Definitions

- 12. Package Dimensions

- 13. Ordering Information

- 14. References

- 15. Revision History