1 slave, Table 3. mclk/lrck ratios, 2 master – Cirrus Logic CS42L51 User Manual

Page 39: Figure 17. master mode timing, 1 slave 4.5.2 master, Figure 17.master mode timing, Cs42l51

DS679F1

39

CS42L51

4.5.1

Slave

LRCK and SCLK are inputs in Slave Mode. The speed of the CODEC is automatically determined based

on the input MCLK/LRCK ratio when the Auto-Detect function is enabled. Certain input clock ratios will

then require an internal divide-by-two of MCLK* using either the MCLKDIV2 bit or the MCLKDIV2 stand-

alone control pin.

Additional clock ratios are allowed when the Auto-Detect function is disabled; but the appropriate speed

mode must be selected using the SPEED[1:0] bits.

4.5.2

Master

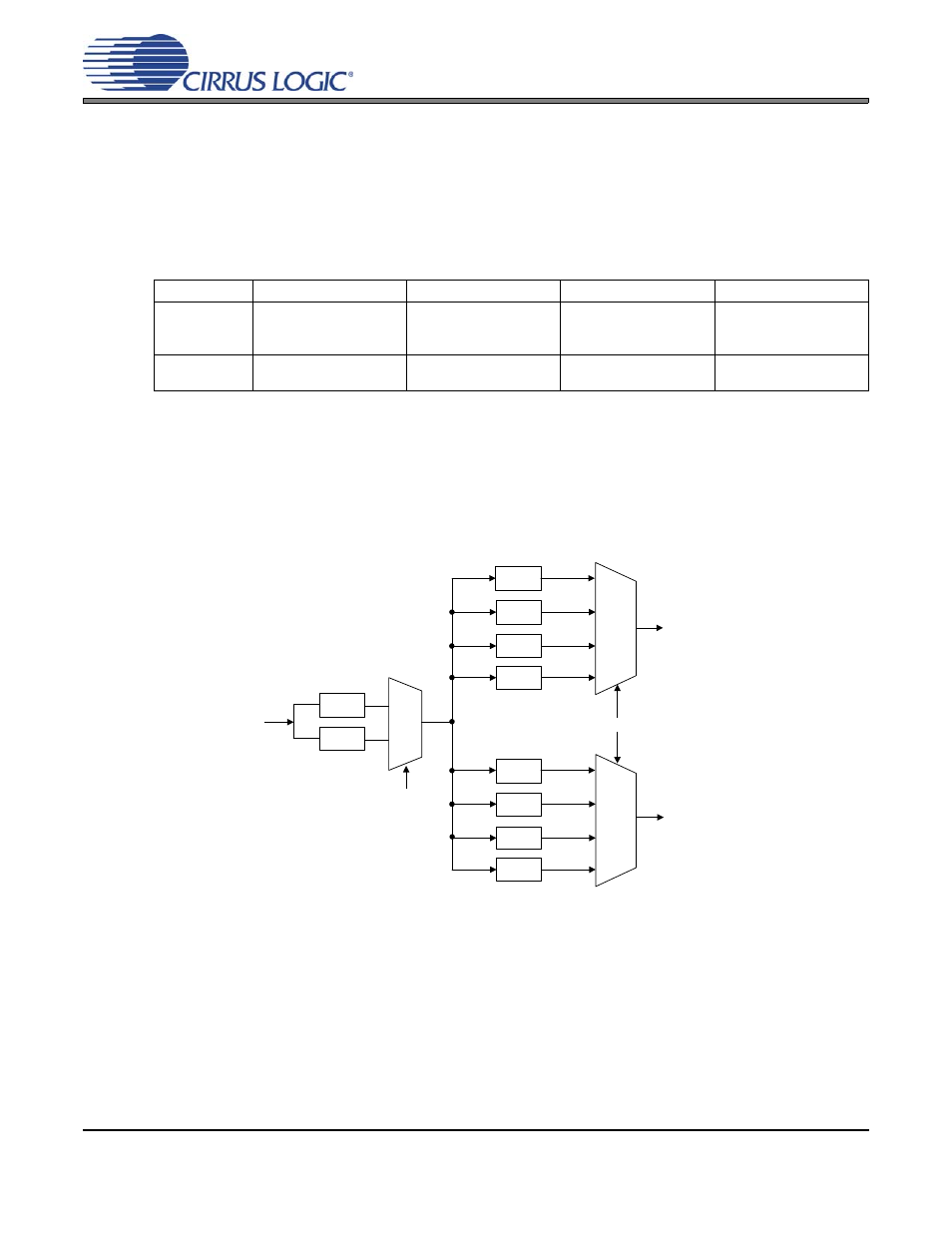

LRCK and SCLK are internally derived from the internal MCLK (after the divide, if MCLKDIV2 is enabled).

In Hardware Mode the CODEC operates in single-speed only. In Software Mode, the CODEC operates

in either quarter-, half-, single- or double-speed depending on the setting of the SPEED[1:0] bits.

Auto-Detect

QSM

HSM

SSM

DSM

Disabled

(Software

Mode only)

512, 768, 1024, 1536,

2048, 3072

256, 384, 512, 768,

1024, 1536

128, 192, 256, 384,

512, 768

128, 192, 256, 384

Enabled

1024, 1536, 2048*,

3072*

512, 768, 1024*, 1536*

256, 384, 512*, 768*

128, 192, 256*, 384*

*MCLKDIV2 must be enabled.

Table 3. MCLK/LRCK Ratios

ч 256

ч 128

ч 512

LRCK Output

(Equal to Fs)

Single

Speed

Quarter

Speed

Half

Speed

01

10

11

SCLK Output

ч 2

ч 1

0

1

MCLK

MCLKDIV2

ч 128

00

ч 4

ч 2

ч 8

Single

Speed

Quarter

Speed

Half

Speed

01

10

11

÷ 2

00

Double

Speed

Double

Speed

SPEED[1:0]

Figure 17. Master Mode Timing