P 60, Cs42l51 – Cirrus Logic CS42L51 User Manual

Page 60

60

DS679F1

CS42L51

ALCX Zero Cross Disable (ALCX_ZCDIS)

Default: 0

0 - Off

1 - On

Function:

Overrides the ZCROSSx bit setting for the ADC. When this bit is set, the ALC attack rate in the PGA will not

be dictated by the zero cross setting. ALC volume-level changes will take effect immediately in one step.

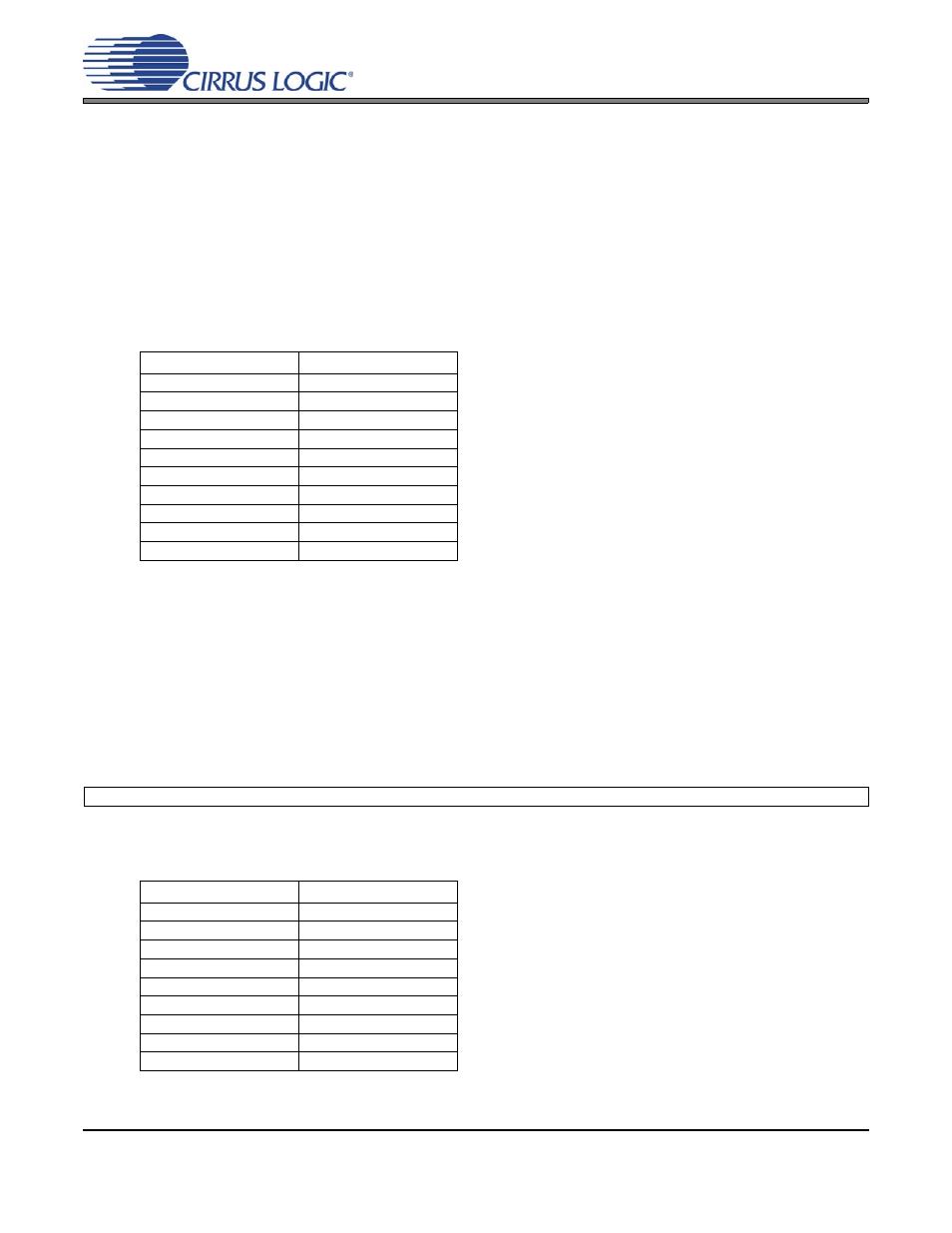

PGA X Gain Control (PGAX_VOL[4:0])

Default: 00000

Function:

The PGAx Gain Control register allows independent setting of the signal levels in 0.5 dB increments as dic-

tated by the ADCx Soft and Zero Cross bits (SOFTx & ZCROSSx) from +12 dB to -3 dB. Gain settings are

decoded as shown in the table above. The gain changes are implemented as dictated by the ALCX Soft &

Zero Cross bits (ALCX_SZC). Levels are decoded as described in the table above.

Note:

When the ALC is enabled, the PGA is automatically controlled and should not be adjusted manu-

ally.

6.11

ADCx Attenuator: ADCA (Address 0Ch) & ADCB (Address 0Dh)

ADCX Attenuation Control (ADCX_ATT[7:0])

Default: 00h

Binary Code

Volume Setting

11000

+12 dB

···

···

01010

+5 dB

···

···

00000

0 dB

11111

-0.5 dB

11110

-1 dB

···

···

11001

-3 dB

11010

-3 dB

7

6

5

4

3

2

1

0

ADCx_ATT7

ADCx_ATT6

ADCx_ATT5

ADCx_ATT4

ADCx_ATT3

ADCx_ATT2

ADCx_ATT1

ADCx_ATT0

Binary Code

Volume Setting

0111 1111

0 dB

···

···

0000 0000

0 dB

1111 1111

-1 dB

1111 1110

-2 dB

···

···

1010 0000

-96 dB

···

···

1000 0000

-96 dB