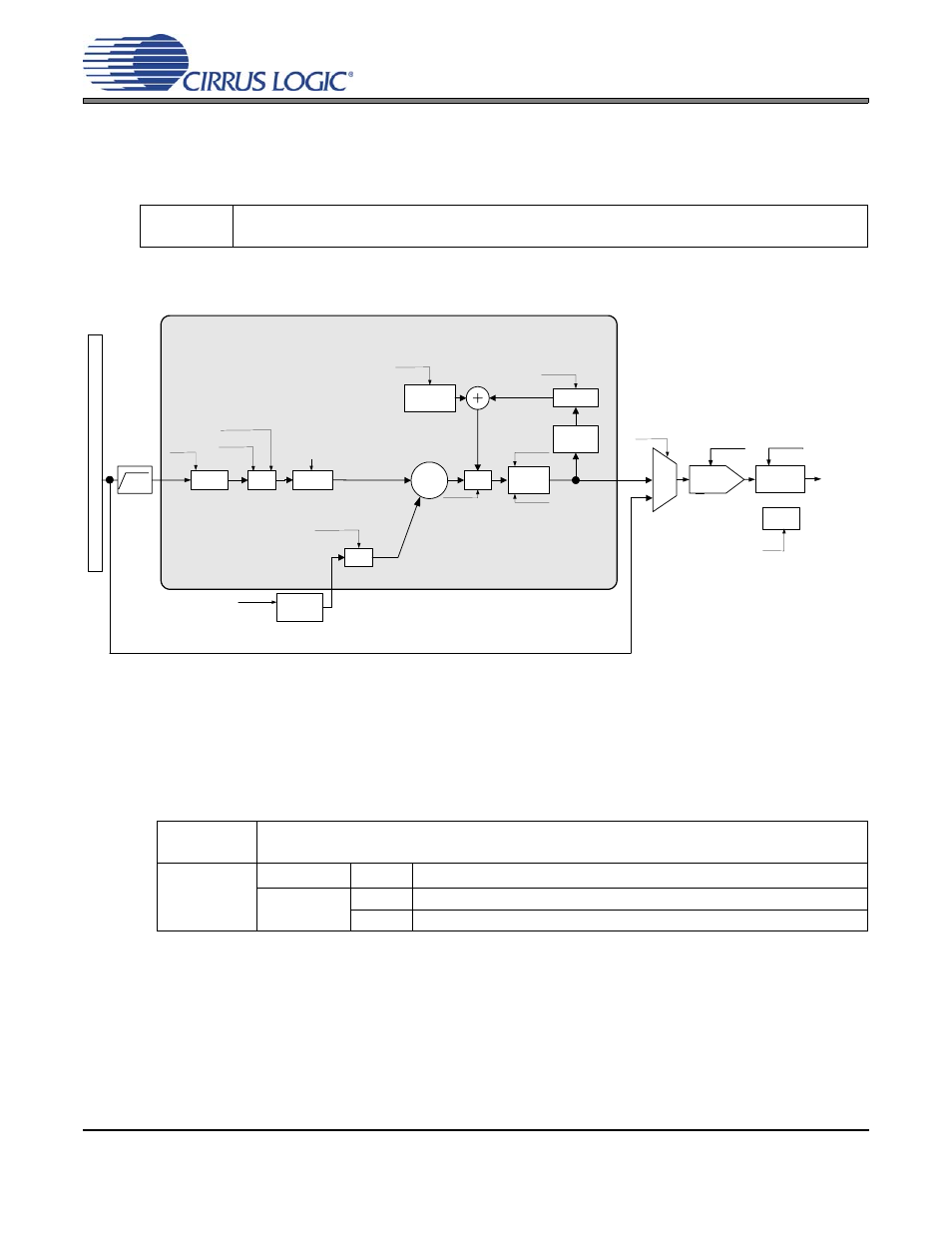

4 analog outputs, Figure 13. output architecture, 1 de-emphasis filter – Cirrus Logic CS42L51 User Manual

Page 34: Figure 13.output architecture, See section, Cs42l51, No de-emphasis, De-emphasis applied

34

DS679F1

CS42L51

4.4

Analog Outputs

AOUTA and AOUTB are the ground-centered line or headphone outputs. Various signal processing options

are available, including digital mixes with the ADC signal and an internal Beep Generator. The desired path

to the DAC must be selected using the DATA_SEL[1:0] bits.

4.4.1

De-Emphasis Filter

The CODEC includes on-chip digital de-emphasis optimized for a sample rate of 44.1 kHz. The filter re-

sponse is shown in

. The de-emphasis feature is included to accommodate audio recordings

that utilize 50/15

µs pre-emphasis equalization as a means of noise reduction. De-emphasis is only avail-

able in Single-Speed Mode.

Software

Controls:

“DAC Control (Address 09h)” on page 58

.

Software

Controls:

“DAC Control (Address 09h)” on page 58

.

Hardware

Control:

Pin

Setting

Selection

“DEM” pin 4.

LO

No De-Emphasis

HI

De-Emphasis Applied

Charge

Pump

Left/Right

HP Out

Switched

Capacitor DAC

and Filter

Headphone

Amp - GND

Centered

PDN_DACA

PDN_DACB

DATA_SEL[1:0]

00

CHRG_FREQ[3:0]

01

HP_GAIN[2:0]

Beep

Generator

Bass/

Treble/

Control

Σ

VOL

Peak

Detect

Limiter

Chnl Vol.

Settings

Demph

VOL

VOL

+12dB/-102dB

0.5dB steps

OUTA_VOL[7:0]

OUTB_VOL[7:0]

+12dB/-51.5dB

0.5dB steps

PCMMIXA_VOL[6:0]

PCMMIXB_VOL[6:0]

0dB/-50dB

2.0dB steps

BPVOL[4:0]

MUTE_PCMMIXA

MUTE_PCMMIXB

DEEMPH

BASS[3:0]

TREB[3:0]

+12.0dB/-10.5dB

1.5dB steps

BASS_CF[1:0]

TREB_CF[1:0]

TC_EN

SIGNAL PROCESSING ENGINE (SPE)

DAC_SZC[1:0]

DACA_MUTE

DACB_MUTE

INV_DACA

INV_DACB

DAC_SNGVOL

AMUTE

ARATE[7:0]

RRATE[7:0]

MAX[2:0]

MIN[2:0]

LIM_SRDIS

LIM_ZCDIS

LIMIT_EN

PCMA[1:0]

PCMB[1:0]

PCM

Serial

Int

e

rf

a

c

e

OFFTIME[2:0]

ONTIME[3:0]

FREQ[3:0]

REPEAT

BEEP

Channel

Swap

Figure 13. Output Architecture