8 on-chip charge pump, 5 serial port clocking, Cs42l51 – Cirrus Logic CS42L51 User Manual

Page 38

38

DS679F1

CS42L51

4.4.8

On-Chip Charge Pump

An on-chip charge pump derives a negative supply voltage from the VA_HP supply. This provides dual

rail supplies allowing a full-scale output swing centered around ground and eliminates the need for large,

DC-blocking capacitors. Added benefits include greater pop suppression and improved low frequency

(bass) response.

Note: Series resistance in the path of the power supplies must be avoided. Any voltage

drop on the VA_HP supply will directly impact the derived negative voltage on the charge pump supply,

VSS_HP, and may result in clipping.

The FLYN and FLYP pins connect to internal switches that charges and discharges the external capacitor

attached, at a default switching frequency. This frequency may be adjusted in the control port registers.

Increasing the charge-pumping capacitor will slightly decease the pumping frequency. The capacitor con-

nected to VSS_HP acts as a charge reservoir for the negative supply as well as a filter for the ripple in-

duced by the charge pump. Increasing this capacitor will decrease the ripple on VSS_HP. Refer to the

typical connection diagrams in

or

values for the charge pump circuitry.

4.5

Serial Port Clocking

The CODEC serial audio interface port operates either as a slave or master. It accepts externally generated

clocks in slave mode and will generate synchronous clocks derived from an input master clock (MCLK) in

master mode.

The frequency of the MCLK must be an integer multiple of, and synchronous with, the system sample rate,

Fs. The LRCK frequency is equal to Fs, the frequency at which audio samples for each channel are clocked

into or out of the device.

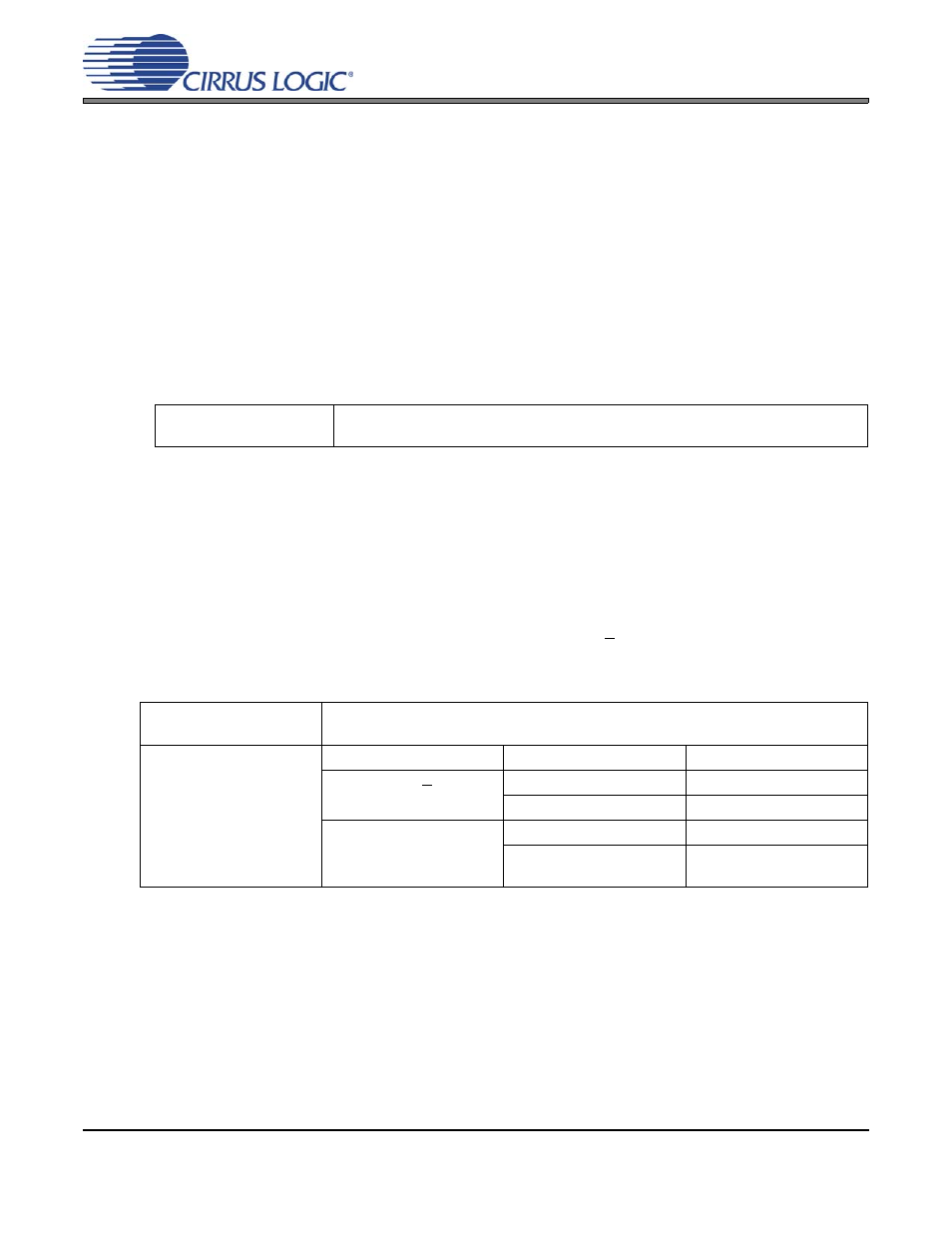

The SPEED and MCLKDIV2 software control bits or the SDOUT/(M/S) and MCLKDIV2 stand-alone control

pins, configure the device to generate the proper clocks in Master Mode and receive the proper clocks in

Slave Mode. The value on the SDOUT pin is latched immediately after powering up in Hardware Mode.

Software

Controls:

“Charge Pump Frequency (Address 21h)” on page 74

Software

Control:

“MIC Power Control & Speed Control (Address 03h)” on page 50

.

Hardware

Control:

Pin

Setting

Selection

“SDOUT, M/S” pin 29

47 k

Ω Pull-down

Slave

47 k

Ω Pull-up

Master

“MCLKDIV2” pin 2

LO

No Divide

HI

MCLK is divided by 2 prior

to all internal circuitry.