Ati sb400/sb600/sb700, Ati rs480 – AMD SimNow Simulator 4.4.4 User Manual

Page 264

AMD Confidential

User Manual

September 12

h

, 2008

252

Appendix A

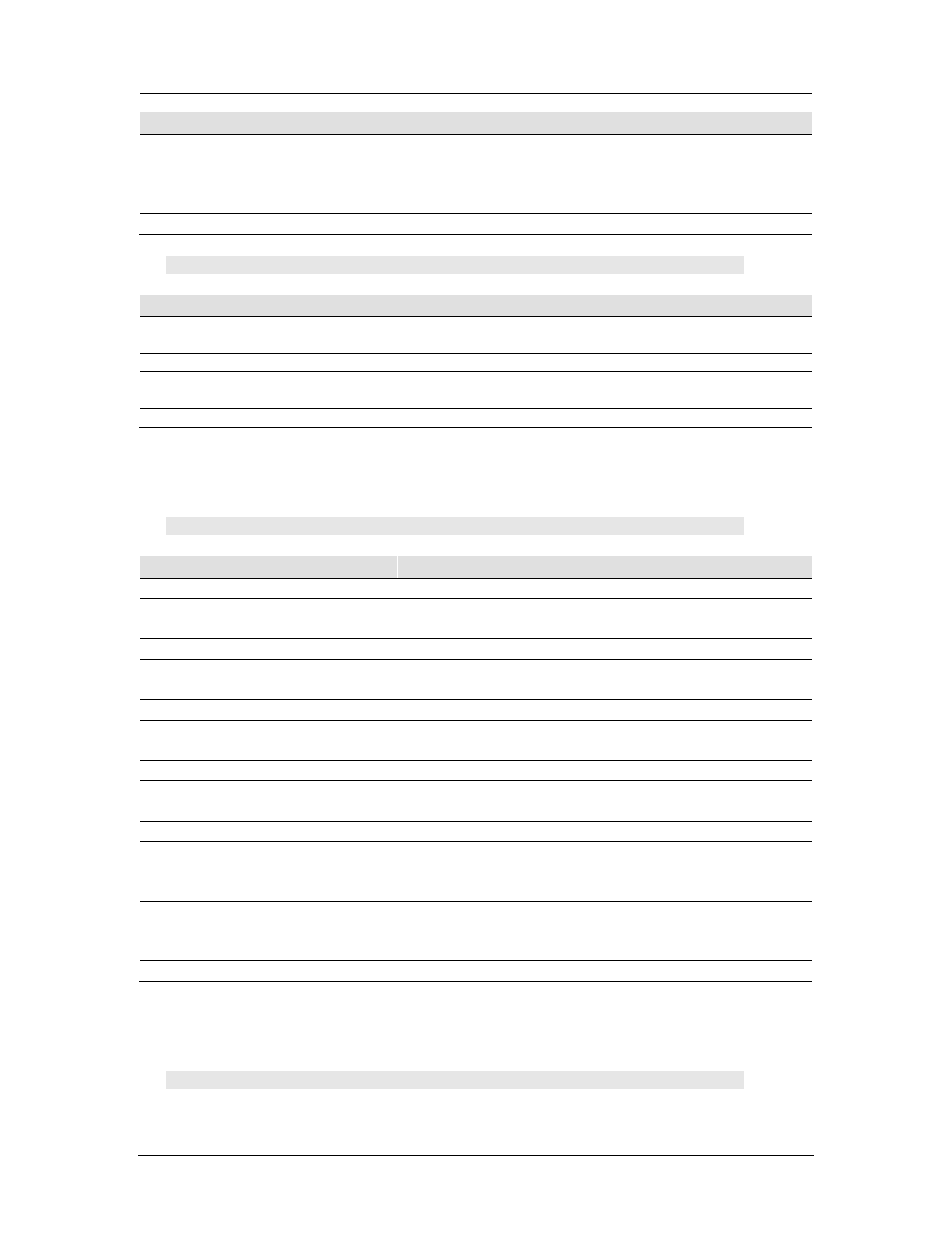

Automation Command

Description

xtrlogfile

Sets name of the log file where XTR

messages should be logged. This is

optional and if not used the log is directed

to the simulators log.

status

Displays the status of XTR playback

1 simnow> xtrsvc.usage

Automation Command

Description

xtrenable <0|1>

Enables (1) or Disables (0) XTR Record.

All other values are invalid.

xtrfile

Sets the XTR-XML file for XTR Record.

XTRMemBits n

Sets number of bits for memory address

bits to scan. n= 16, 32 or 48. Default is 32.

Xtrstatus

Displays the status of XTR Record.

A.7.29 ATI SB400/SB600/SB700

1 simnow> sb600.usage

Automation Command

Description

HtInterrupts (0|1)

Enables (1) or disables (0) HyperTransport interrupts.

HtIntStatus

Returns „enabled‟ if HyperTransport interrupts are

enabled; otherwise it returns „disabled‟.

IoLog (0|1)

Enables (1) or disables (0) IO logging.

IoLogStatus

Returns „enabled‟ if IO Logging is enabled; otherwise it

returns „disabled‟.

MemLog (0|1)

Enables (1) or disables (0) IO logging.

MemLogStatus

Returns „enabled‟ if Memory Logging is enabled;

otherwise it returns „disabled‟.

SmiSciLog (0|1)

Enables (1) or disables (0) IO logging.

SmiSciLogStatus

Returns „enabled‟ if SMI SCI Logging is enabled;

otherwise it returns „disabled‟.

Version

Displays the binary revision of the RD790 model.

SetPciIrqMap {BasePciIrq(0-3)}

{ChipPciIrq(0-7)}

Depending on platform configuration, it maps base

PCIIRQ#A/B/C/D (0-3) from PCI bridge to ATI chip

internal PCIIRQ#A/B/C/D/E/F/G/H (0-7).

GetPciIrqMap {BasePciIrq(0-3)}

Returns

the

ATI

chip

internal

PCIIRQ#A/B/C/D/E/F/G/H (0-7) which the specific

base PCIIRQ#A/B/C/D(0-3) is mapped to.

GetPciIrqTotal

Returns the total number of chip internal PCIIRQs.

A.7.30 ATI RS480

1 simnow> rs780.usage