Virtualization instruction reference, Bit media instruction reference, 3dnow!™ instruction set – AMD SimNow Simulator 4.4.4 User Manual

Page 236: A.6.4 virtualization instruction reference, A.6.5 64-bit media instruction reference, A.6.6 3dn ow!™ instruction set, Amd confidential user manual september 12

AMD Confidential

User Manual

September 12

h

, 2008

224

Appendix A

A.6.4

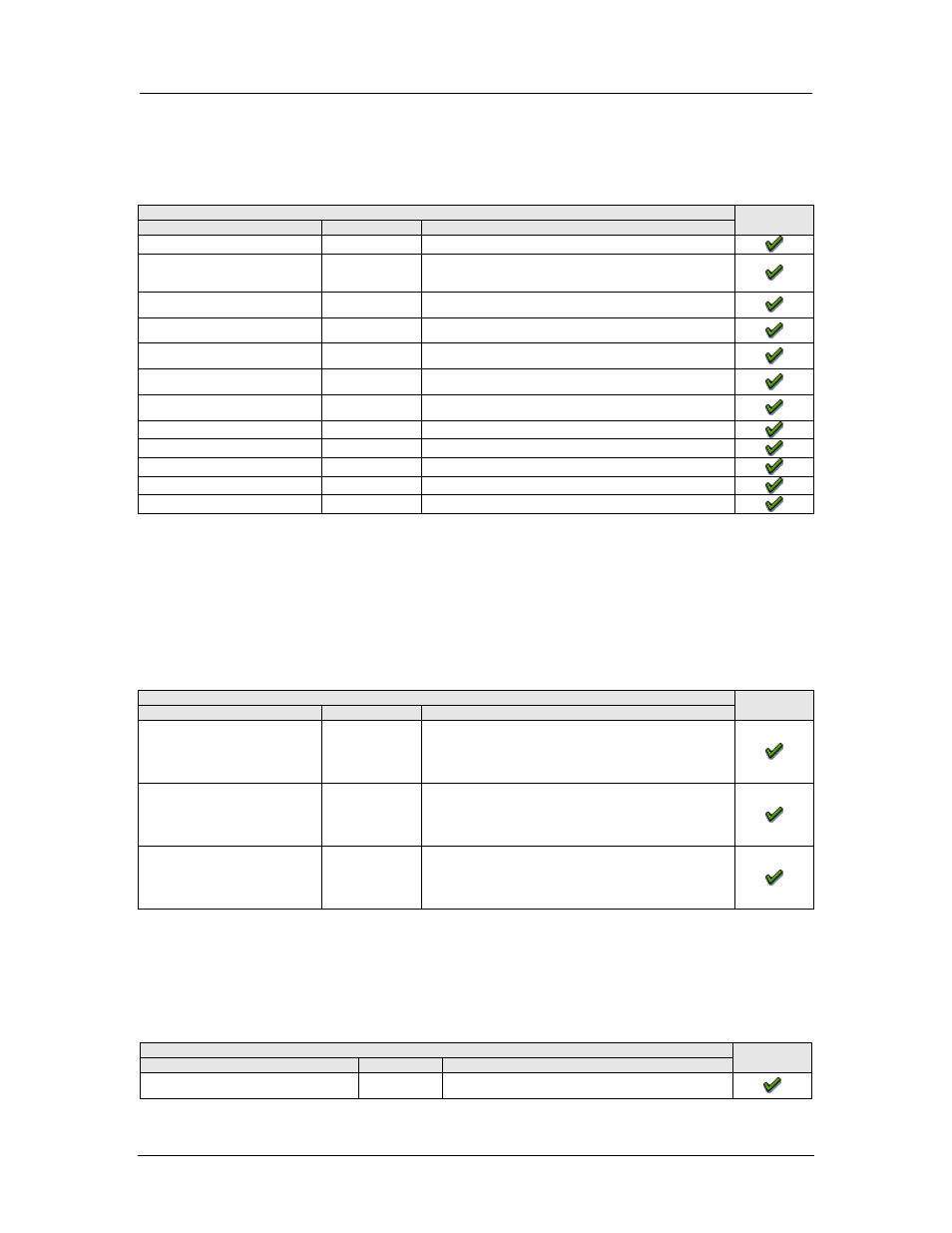

Virtualization Instruction Reference

For more information on Virtualization Technology, see AMD Publication #33047,

AMD64 Virtualization Technology.

Instruction

Supported

Mnemonic

Opcode

Description

CLGI

0F 01 DD

Clear Global Interrupt Flag.

INVLPGA

0F 01 DF

Invalidates the TLB mapping for the

virtual page specified in rAX and the

ASID specified in ECX.

MOV reg32,CR8

F0 20 /r

Alternate notation for move from CR8 to

register.

MOV reg64,CR8

F0 20 /r

Alternate notation for move register to

CR8.

MOV CR8,reg32

F0 22 /r

Alternate notation for move from CR8 to

register.

MOV CR8,reg64

F0 22 /r

Alternate notation for move register to

CR8.

SKINIT

0F 01 DE

Secure initialization and jump, with

attestation.

STGI

0F 01 DC

Set Global Interrupt Flag.

VMLOAD

0F 01 DA

Load State from VMCB.

VMCALL

0F 01 D9

Call VMM.

VMRUN

0F 01 D8

Run Virtual Machine.

VMSAVE

0F 01 DB

Save State to VMCB.

A.6.5 64-Bit Media Instruction Reference

These instructions described in this section operate on data located in the 64-bit MMX

registers. Most of the instructions operate in parallel on sets of packed elements called

vectors, although some operate on scalars. The instructions define both integer and

floating-point operations, and include the legacy MMX instructions and the AMD

extensions to the MMX instruction set.

Instruction

Supported

Mnemonic

Opcode

Description

CVTPD2PI mmx,xmm2/m128 66 0F 2D /r

Converts

packed

double-precision

floating-point

values

in

an

XMM

register or 128-bit memory location to

packed doubleword integers values in

the destination MMX™ register.

CVTPI2PD xmm,mmx/m64

66 0F 2A /r

Converts two packed doubleword integer

values in a MMX™ register or 64-bit

memory location to two packed double-

precision floating-point values in the

destination XMM register.

CVTPI2PS mmx,xmm2/m128 0F 2A /r

Converts

packed

doubleword

integer

values in a MMX™ register or 64-bit

memory location to single-precision

floating-point

values

in

the

destination XMM register.

A.6.6 3DN

ow!™ Instruction Set

This chapter describes the 3DNow! Instruction Set that the simulator supports and

simulates. 3DNow! Technology is a group of new instructions that opens the traditional

processing bottlenecks for floating-point-intensive and multimedia applications.

Instruction

Supported

Mnemonic

Opcode

Description

FEMMS

0F 0E

Fast Enter/Exit of the MMX or

floating-point state.