Extension to the 3dnow! instruction set, Prescott new instructions, A.6.7 extension to the 3dnow! instruction set – AMD SimNow Simulator 4.4.4 User Manual

Page 237: A.6.8 prescott new instructions, Amd confidential user manual september 12

AMD Confidential

User Manual

September 12

th

, 2008

Appendix A

225

Instruction

Supported

Mnemonic

Opcode

Description

PAVGUSB mmreg1,mmreg2/m64

0F 0F /BF Average of unsigned packed 8-bit

values.

PF2ID mmreg1,mmreg2/m64

0F 0F /1D Converts

packed

floating-point

operand or packed 32-bit integer.

PFACC mmreg1,mmreg2/m64

0F 0F /AE Floating-point accumulate.

PFADD mmreg1,mmreg2/m64

0F 0F /9E Packed, floating-point addition.

PFCMPEQ mmreg1,mmreg2/m64

0F 0F /B0 Packed

floating-point

comparison,

equal to.

PFCMPPGE mmreg1,mmreg2/m64

0F 0F /90 Packed

floating-point

comparison,

greater than or equal to.

PFCMPGT mmreg1,mmreg2/m64

0F 0F /A0 Packed

floating-point

comparison,

greater than.

PFMAX mmreg1,mmreg2/m64

0F 0F /A4 Packed floating-point maximum.

PFMIN mmreg1,mmreg2/m64

0F 0F /94 Packed floating-point minimum.

PFMUL mmreg1,mmreg2/m64

0F 0F /B4 Packed

floating-point

multiplication.

PFRCP mmreg1,mmreg2/m64

0F 0F /96 Packed floating-point approximation.

PFRCPIT1 mmreg1,mmreg2/m64

0F 0F /A6 Packed

floating-point

reciprocal,

first iteration step.

PFRCPIT2 mmreg1,mmreg2/m64

0F 0F /B6 Packed

floating-point

reciprocal,

second iteration step.

PFRSQIT1 mmreg1,mmreg2/m64

0F 0F /A7 Packed

floating-point

reciprocal,

square root, first iteration step.

PFRSQRT mmreg1,mmreg2/m64

0F 0F /97 Packed

floating-point

reciprocal,

square root approximation.

PFSUB mmreg1,mmreg2/m64

0F 0F /9A Packed, floating-point subtraction.

PFSUBR mmreg1,mmreg2/m64

0F 0F /AA Packed,

floating-point

reverse

subtraction.

PI2FD mmreg1,mmreg2/m64

0F 0F /0D Packed 32-bit integer to floating-

point conversion.

PMULHRW mmreg1,mmreg2/m64

0F 0F /B7

Multiply signed packed 16-bit values

with rounding and store the high 16

bits.

PREFETCH/PREFETCHW

0F 0D

Prefetch processor cache line into

L1 data cache (Dcache).

Table 15-10: 3DNow!™ Instruction Reference

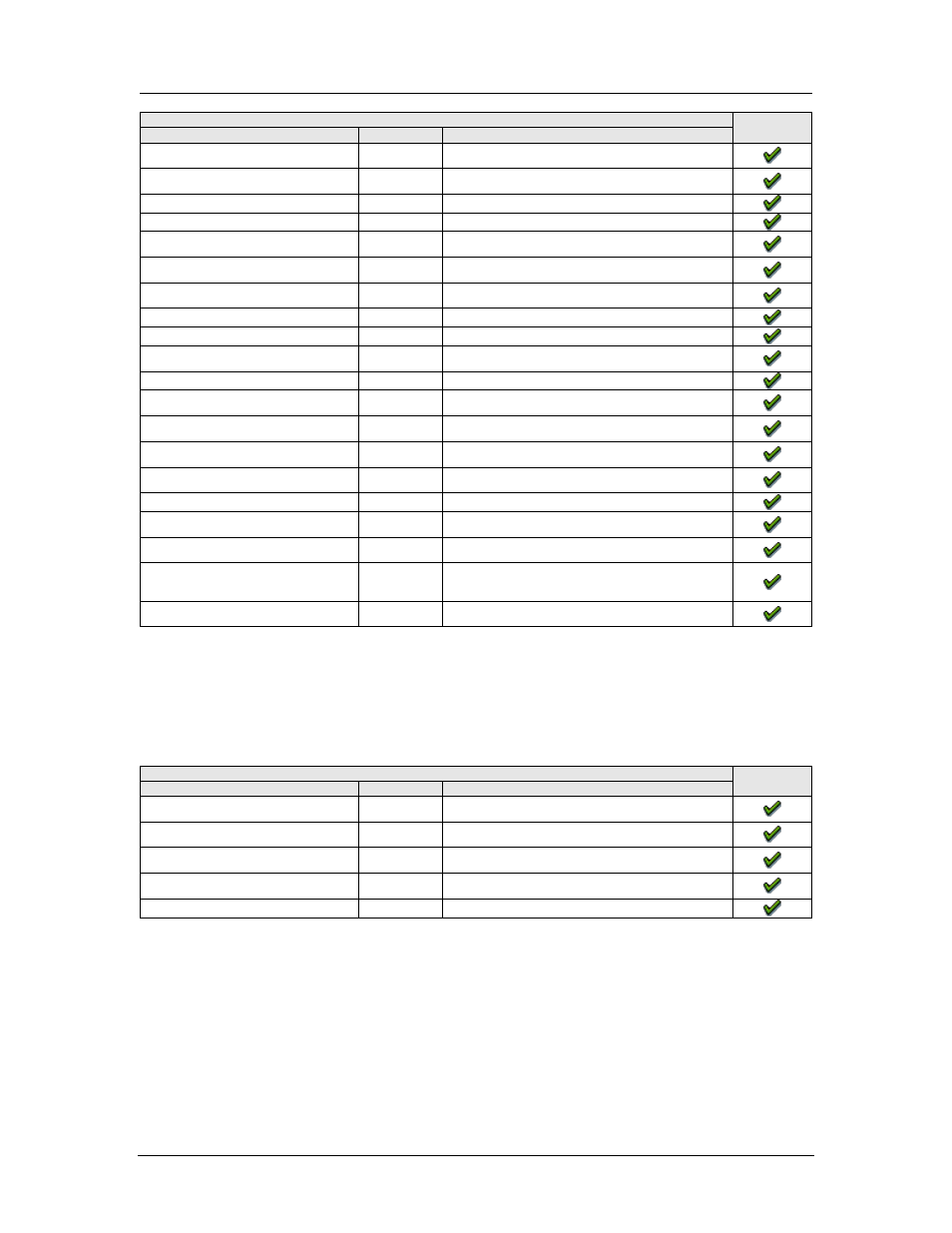

A.6.7 Extension to the 3DNow! Instruction Set

This section describes the five new DSP instructions added to the 3DNow! Instruction

set.

Instruction

Supported

Mnemonic

Opcode

Description

PF2IW mmreg1,mmreg2/m64

0F 0F /1C Packed floating-point to integer

word conversion with sign extend.

PFNACC mmreg1,mmreg2/m64

0F 0F /8A Packed

floating-point

negative

accumulate.

PFPNACC mmreg1,mmreg2/m64

0F 0F /8E Packed

floating-point

mixed

positive-negative accumulate.

PI2FW mmreg1,mmreg2/m64

0F 0F /0C Packed 16-bit integer to floating-

point conversion.

PSWAPD mmreg1,mmreg2/m64

0F 0F /BB Packed swap double word.

Table 15-11: Extension to 3DNow! Instruction Reference

A.6.8 Prescott New Instructions

Prescott New Instruction technology for the x64 architecture is a set of 13 new

instructions that accelerate performance of Streaming SIMD Extension technology,

Streaming SIMD Extension 2 technology, and x87-FP math capabilities. The new

technology is compatible with existing software and should run correctly, without

modification. The thirteen new instructions are summarized in the following section. For

detailed information on each instruction refer to a complete Instruction Set Reference.