Amd confidential user manual september 12 – AMD SimNow Simulator 4.4.4 User Manual

Page 231

AMD Confidential

User Manual

September 12

th

, 2008

Appendix A

219

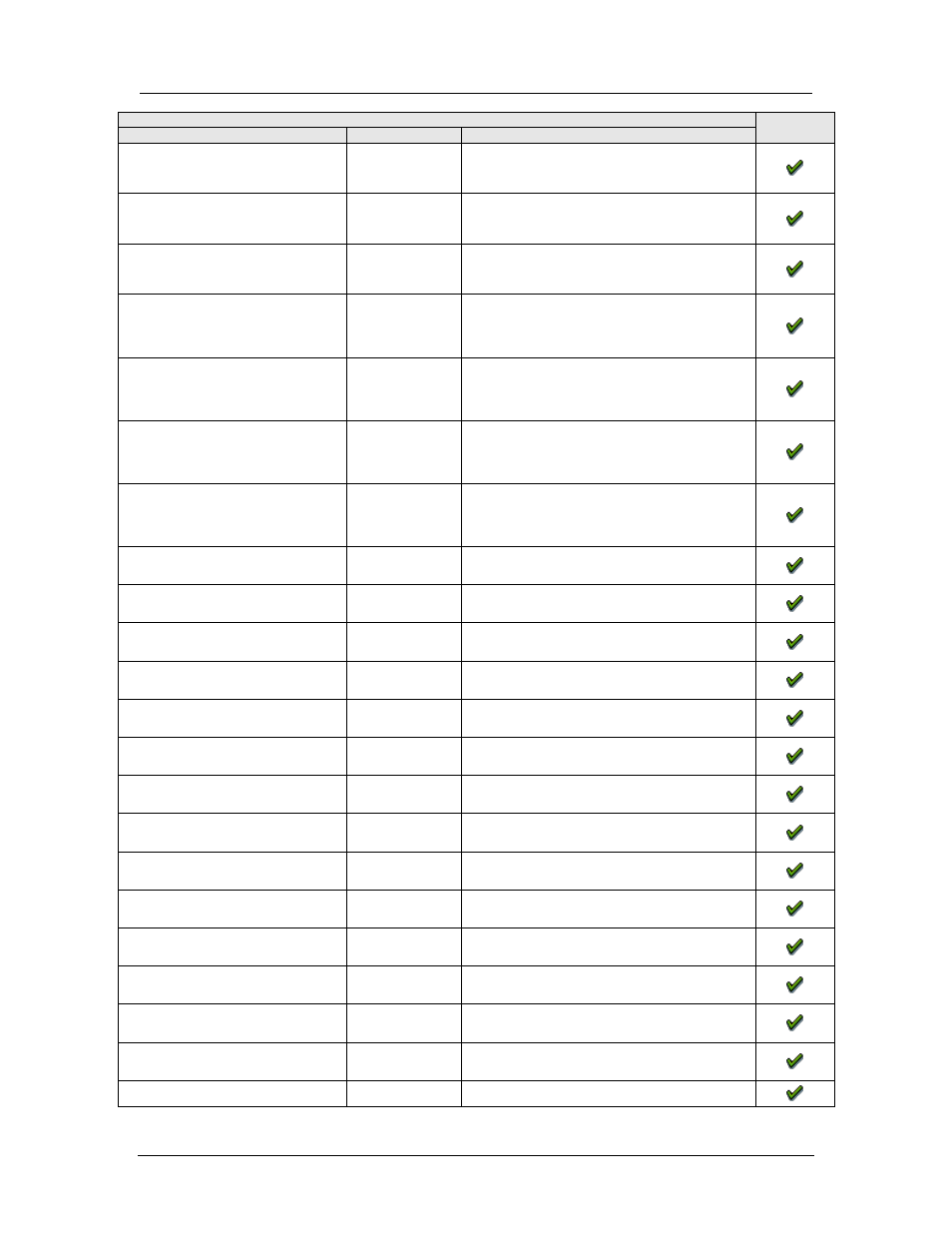

Instruction

Supported

Mnemonic

Opcode

Description

TEST reg/mem16,reg16

85 /r

AND the contents of a 16-bit register

with the contents of a 16-bit

register or memory operand and set

rFLAGS to reflect the result.

TEST reg/mem32,reg32

85 /r

AND the contents of a 32-bit register

with the contents of a 32-bit

register or memory operand and set

rFLAGS to reflect the result.

TEST reg/mem64,reg64

85 /r

AND the contents of a 64-bit register

with the contents of a 64-bit

register or memory operand and set

rFLAGS to reflect the result.

XADD reg/mem8,reg8

0F C0 /r

Exchange the contents of an 8-bit

register with the contents of 8-bit

destination

register

or

memory

operand and load their sum into the

destination.

XADD reg/mem16,reg16

0F C1 /r

Exchange the contents of a 16-bit

register with the contents of 16-bit

destination

register

or

memory

operand and load their sum into the

destination.

XADD reg/mem32,reg32

0F C1 /r

Exchange the contents of a 32-bit

register with the contents of 32-bit

destination

register

or

memory

operand and load their sum into the

destination.

XADD reg/mem64,reg64

0F C1 /r

Exchange the contents of a 64-bit

register with the contents of 64-bit

destination

register

or

memory

operand and load their sum into the

destination.

XCHG AX,reg16

90 +rw

Exchange the contents of AX register

with the contents of a 16-bit

register.

XCHG reg16,AX

90 +rw

Exchange the contents of a 16-bit

register with the contents of the AX

register.

XCHG AX,reg32

90 +rd

Exchange the contents of EAX register

with the contents of a 32-bit

register.

XCHG reg32,AX

90 +rd

Exchange the contents of a 32-bit

register with the contents of the EAX

register.

XCHG RAX,reg64

90 +rq

Exchange the contents of RAX register

with the contents of a 64-bit

register.

XCHG reg64,RAX

90 +rq

Exchange the contents of a 64-bit

register with the contents of the RAX

register.

XCHG reg/mem8,reg8

86 /r

Exchange the contents of an 8-bit

register with the contents of an 8-

bit register or memory operand.

XCHG reg8,reg/mem8

86 /r

Exchange the contents of an 8-bit

register or memory operand with the

contents of an 8-bit register.

XCHG reg/mem16,reg16

87 /r

Exchange the contents of a 16-bit

register with the contents of a 16-

bit register or memory operand.

XCHG reg16,reg/mem16

87 /r

Exchange the contents of a 16-bit

register or memory operand with the

contents of a 16-bit register.

XCHG reg/mem32,reg32

87 /r

Exchange the contents of a 32-bit

register with the contents of a 32-

bit register or memory operand.

XCHG reg32,reg/mem32

87 /r

Exchange the contents of a 32-bit

register or memory operand with the

contents of a 32-bit register.

XCHG reg/mem64,reg64

87 /r

Exchange the contents of a 64-bit

register with the contents of a 64-

bit register or memory operand.

XCHG reg64,reg/mem64

87 /r

Exchange the contents of a 64-bit

register or memory operand with the

contents of a 64-bit register.

XLAT mem8

D7

Set AL to the contents of DS:[rBX +

unsigned AL].