Amd confidential user manual september 12 – AMD SimNow Simulator 4.4.4 User Manual

Page 216

AMD Confidential

User Manual

September 12

h

, 2008

204

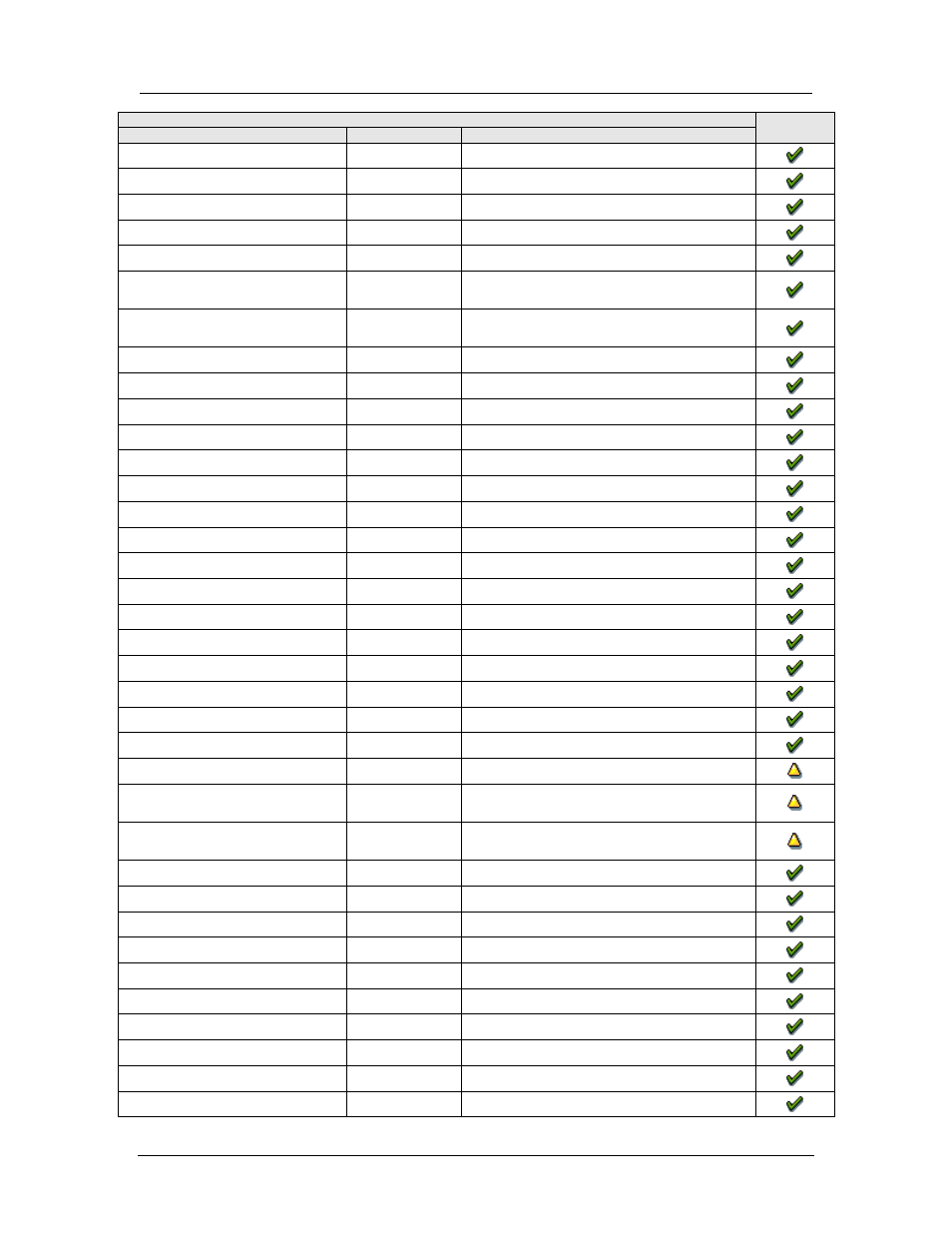

Appendix A

Instruction

Supported

Mnemonic

Opcode

Description

JMP rel16off

E9 cw

Short jump with the target specified

by a 16-bit signed displacement.

JMP rel32off

E9 cd

Short jump with the target specified

by a 32-bit signed displacement.

JMP reg/mem16

FF /4

Near jump with the target specified

reg/mem16.

JMP reg/mem32

FF /4

Near jump with the target specified

reg/mem32.

JMP reg/mem64

FF /4

Near jump with the target specified

reg/mem64.

JMP FAR pntr16:16

EA cd

Far jump direct, with the target

specified by a far pointer contained

in the instruction.

JMP FAR pntr16:32

EA cp

Far jump direct, with the target

specified by a far pointer contained

in the instruction.

JMP FAR mem16:16

FF /5

Far jump indirect, with the target

specified by a far pointer in memory.

JMP FAR mem16:32

FF /5

Far jump indirect, with the target

specified by a far pointer in memory.

LAHF

9F

Load the SF, ZF, AF, PF, and CF flags

into the AH register.

LDS reg16,mem16:16

C5 /r

Load DS:reg16 with a far pointer from

memory.

LDS reg32,mem16:32

C5 /r

Load DS:reg32 with a far pointer from

memory.

LES reg16,mem16:16

C4 /r

Load ES:reg16 with a far pointer from

memory.

LES reg32,mem16:32

C4 /r

Load ES:reg32 with a far pointer from

memory.

LFS reg16,mem16:16

0F B4 /r

Load FS:reg16 with a far pointer from

memory.

LFS reg32,mem16:32

0F B4 /r

Load FS:reg32 with a far pointer from

memory.

LGS reg16,mem16:16

0F B5 /r

Load GS:reg16 with a far pointer from

memory.

LGS reg32,mem16:32

0F B5 /r

Load GS:reg32 with a far pointer from

memory.

LSS reg16,mem16:16

0F B2 /r

Load SS:reg16 with a far pointer from

memory.

LSS reg32,mem16:32

0F B2 /r

Load SS:reg32 with a far pointer from

memory.

LEA reg16,mem

8D /r

Store effective address in a 16-bit

register.

LEA reg32,mem

8D /r

Store effective address in a 32-bit

register.

LEA reg64,mem

8D /r

Store effective address in a 64-bit

register.

LEAVE

C9

Set the stack pointer SP to the value

in the BP register and pop BP.

LEAVE

C9

Set the stack pointer ESP to the

value in the EBP register and pop

EBP.

LEAVE

C9

Set the stack pointer RSP to the

value in the RBP register and pop

RBP.

LFENCE

0F AE E8

Force strong ordering of (serialize)

load operations.

LODS mem8

AC

Load byte at DS:rSI into AL and then

increment or decrement rSI.

LODS mem16

AD

Load word at DS:rSI into AX and then

increment or decrement rSI.

LODS mem32

AD

Load doubleword at DS:rSI into EAX

and then increment or decrement rSI.

LODS mem64

AD

Load quadword at DS:rSI into RAX and

then increment or decrement rSI.

LODSB

AC

Load byte at DS:rSI into AL and then

increment or decrement rSI.

LODSW

AD

Load word at DS:rSI into AX and then

increment or decrement rSI.

LODSD

AD

Load doubleword at DS:rSI into EAX

and then increment or decrement rSI.

LODSQ

AD

Load quadword at DS:rSI into RAX and

then increment or decrement rSI.

LOOP rel8off

E2 cb

Decrement rCX and then jump short if

rCX is not 0.