Amd confidential user manual september 12 – AMD SimNow Simulator 4.4.4 User Manual

Page 234

AMD Confidential

User Manual

September 12

h

, 2008

222

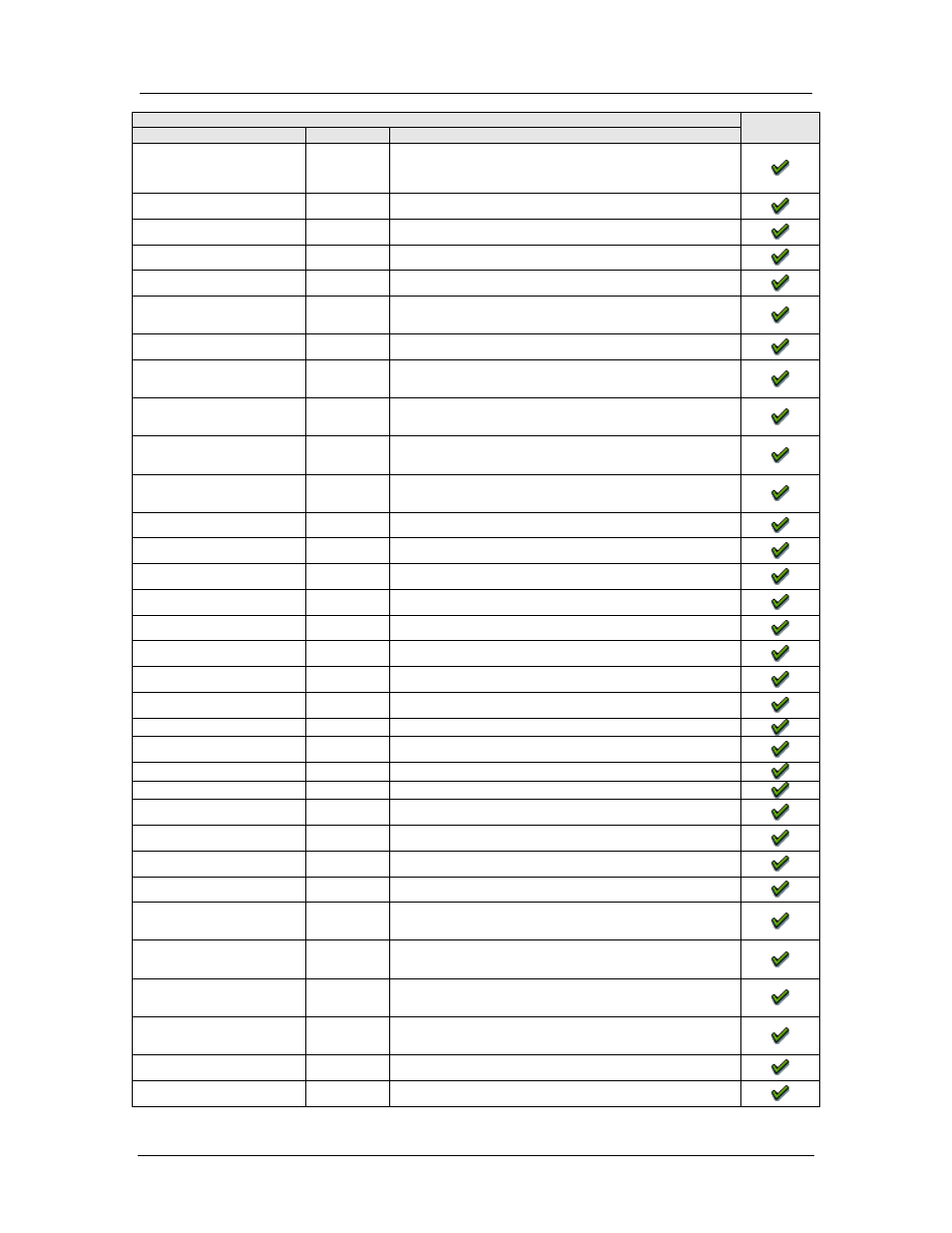

Appendix A

Instruction

Supported

Mnemonic

Opcode

Description

LAR reg64,reg/mem16

0F 02 /r

Reads the GDT/LDT descriptor referenced by

the

16-bit

source

operand,

masks

the

attributes with 00FFFF00h and saves the

result in the 64-bit destination register.

LGDT mem16:32

0F 01 /2

Loads mem16:32 into the global descriptor

table register.

LGDT mem16:64

0F 01 /2

Loads mem16:64 into the global descriptor

table register.

LIDT mem16:32

0F 01 /3

Loads mem16:32 into the interrupt descriptor

table register.

LIDT mem16:64

0F 01 /3

Loads mem16:64 into the interrupt descriptor

table register.

LLDT reg/mem16

0F 00 /2

Load the 16-bit segment selector into the

local descriptor table register and load the

LDT descriptor from the GDT.

LMSW reg/mem16

0F 01 /6

Loads the lower 4 bits of the source into

the lower 4 bits of CR0.

LSL reg16,reg/mem16

0F 03 /r

Loads a 16-bit general-purpose register with

the segment limit or a selector specified in

a 16-bit memory or register operand.

LSL reg32,reg/mem16

0F 03 /r

Loads a 32-bit general-purpose register with

the segment limit or a selector specified in

a 16-bit memory or register operand.

LSL reg64,reg/mem16

0F 03 /r

Loads a 64-bit general-purpose register with

the segment limit or a selector specified in

a 16-bit memory or register operand.

LTR reg/mem16

0F 00 /3

Load the 16-bit segment selector into the

task register and load the TSS descriptor

from the GDT.

MOV CRn,reg32

0F 22 /r

Move the contents of a 32-bit register to

CRn.

MOV CRn,reg64

0F 22 /r

Move the contents of a 64-bit register to

CRn.

MOV reg32,CRn

0F 20 /r

Move the contents of CRn to a 32-bit

register.

MOV reg64,CRn

0F 20 /r

Move the contents of CRn to a 64-bit

register.

MOV DRn,reg32

0F 21 /r

Move the contents of a 32-bit register to

DRn.

MOV DRn,reg64

0F 21 /r

Move the contents of a 64-bit register to

DRn.

MOV reg32,DRn

0F 23 /r

Move the contents of DRn to a 32-bit

register.

MOV reg64,DRn

0F 23 /r

Move the contents of DRn to a 64-bit

register.

RDMSR

0F 32

Copy MSR specified by ECX into EDX:EAX.

RDPMC

0F 33

Copy

the

performance

monitor

counter

specified by ECX into EDX:EAX.

RDTSC

0F 31

Copy the time-stamp counter into EDX:EAX.

RSM

0F AA

Resume operation of an interrupted program.

SGDT mem16:32

0F 01 /0

Store global descriptor table register to

memory.

SGDT mem16:64

0F 01 /0

Store global descriptor table register to

memory.

SIDT mem16:32

0F 01 /1

Store interrupt descriptor table register to

memory.

SIDT mem16:64

0F 01 /1

Store interrupt descriptor table register to

memory.

SLDT reg16

0F 00 /0

Store the segment selector from the local

descriptor table register to a 16-bit

register.

SLDT reg32

0F 00 /0

Store the segment selector from the local

descriptor table register to a 32-bit

register.

SLDT reg64

0F 00 /0

Store the segment selector from the local

descriptor table register to a 64-bit

register.

SLDT mem16

0F 00 /0

Store the segment selector from the local

descriptor table register to a 16-bit memory

location.

SMSW reg16

0F 01 /4

Store the low 16 bits of CR0 to a 16-bit

register.

SMSW reg32

0F 01 /4

Store the low 32 bits of CR0 to a 32-bit

register.