C.9 clear interrupt and fifo - base+8 and base+9, C.10 d/a output channel 0 - base+10 and base+11, C.11 d/a output channel 0 - base+10 and base+11 – B&B Electronics PCI-1711 - Manual User Manual

Page 94: Table c-11: register to clear interrupt and fifo, Table c-12: register for load d/a channel 0 data, Clear interrupt and fifo - base+8 and base+9, Table c-11, Register to clear interrupt and fifo, Appendix c

Appendix C

– 86 –

PCI-1710 series User’s Manual

Advantech Co., Ltd.

www.advantech.com

C.9 Clear Interrupt and FIFO - BASE+8 and BASE+9

Writing data to either of these two bytes clears the interrupt or the

FIFO.

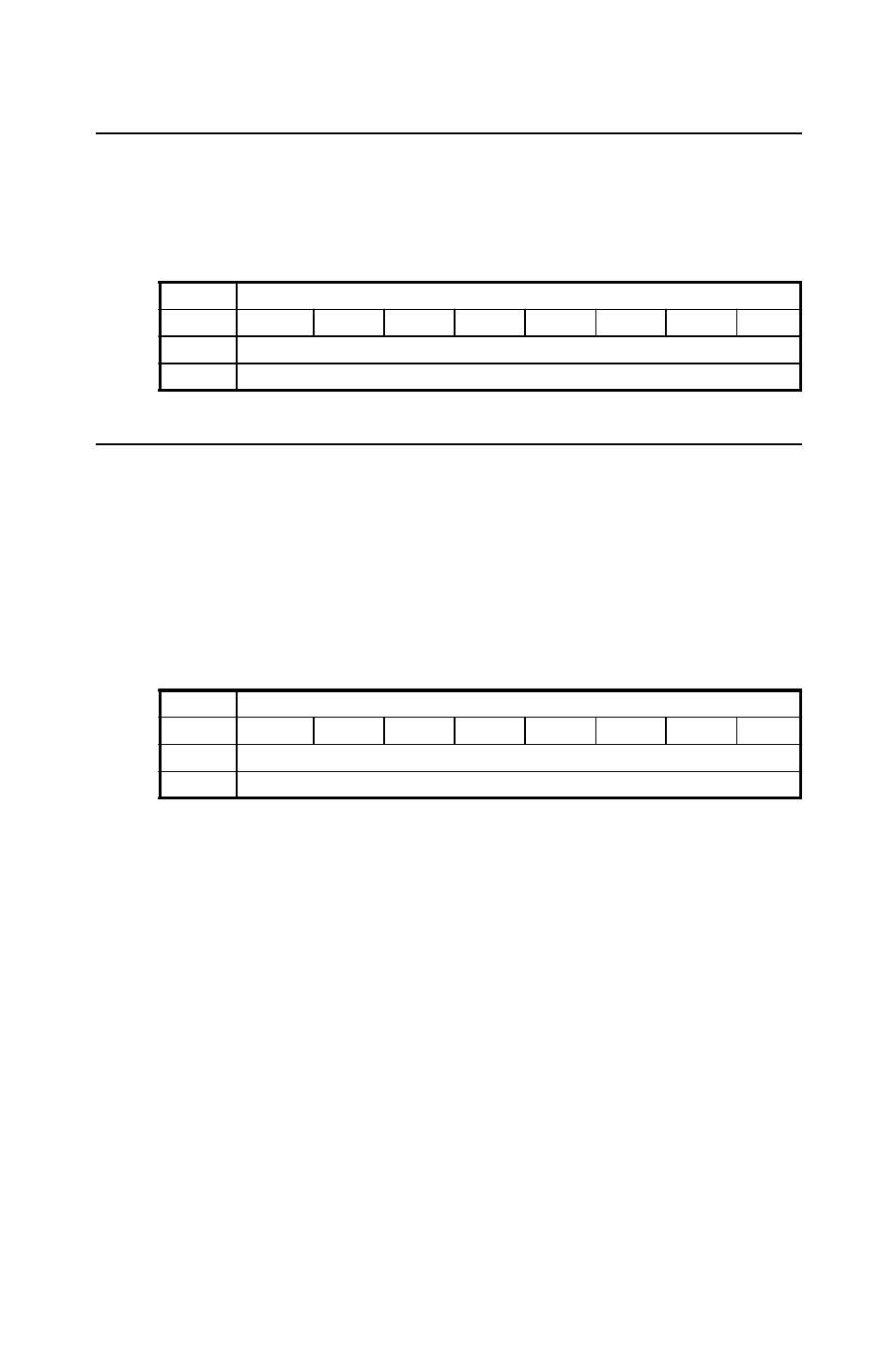

Table C-11: Register to clear interrupt and FIFO

C.10 D/A Output Channel 0 - BASE+10 and BASE+11

The PCI-1716 provides the innovative design as gate control for

Analog Output function. It works as general Analog Output function

when you disable the flag (bit 3 (DA0_LDEN) of BASE+14). That

means the data will be output immediately. However, when you enable

the flag, you need to read these two registers BASE+10 and BASE+11

to output the data to the Analog Output channel.

Table C-12: Register for load D/A channel 0 data

Write

Clear Interrupt and FIFO

Bit #

7

6

5

4

3

2

1

0

BASE + 9

Clear FIFO

BASE + 8

Clear Interrupt

Read

Load D/A Channel 0 data

Bit #

7

6

5

4

3

2

1

0

BASE + 11

BASE + 10