Ssi interrupt, Modulation and demodulation, Internal 2-wire multi-chip link – Rainbow Electronics ATAR862-8 User Manual

Page 73: Atar862-8

73

ATAR862-8

4589B–4BMCU–02/03

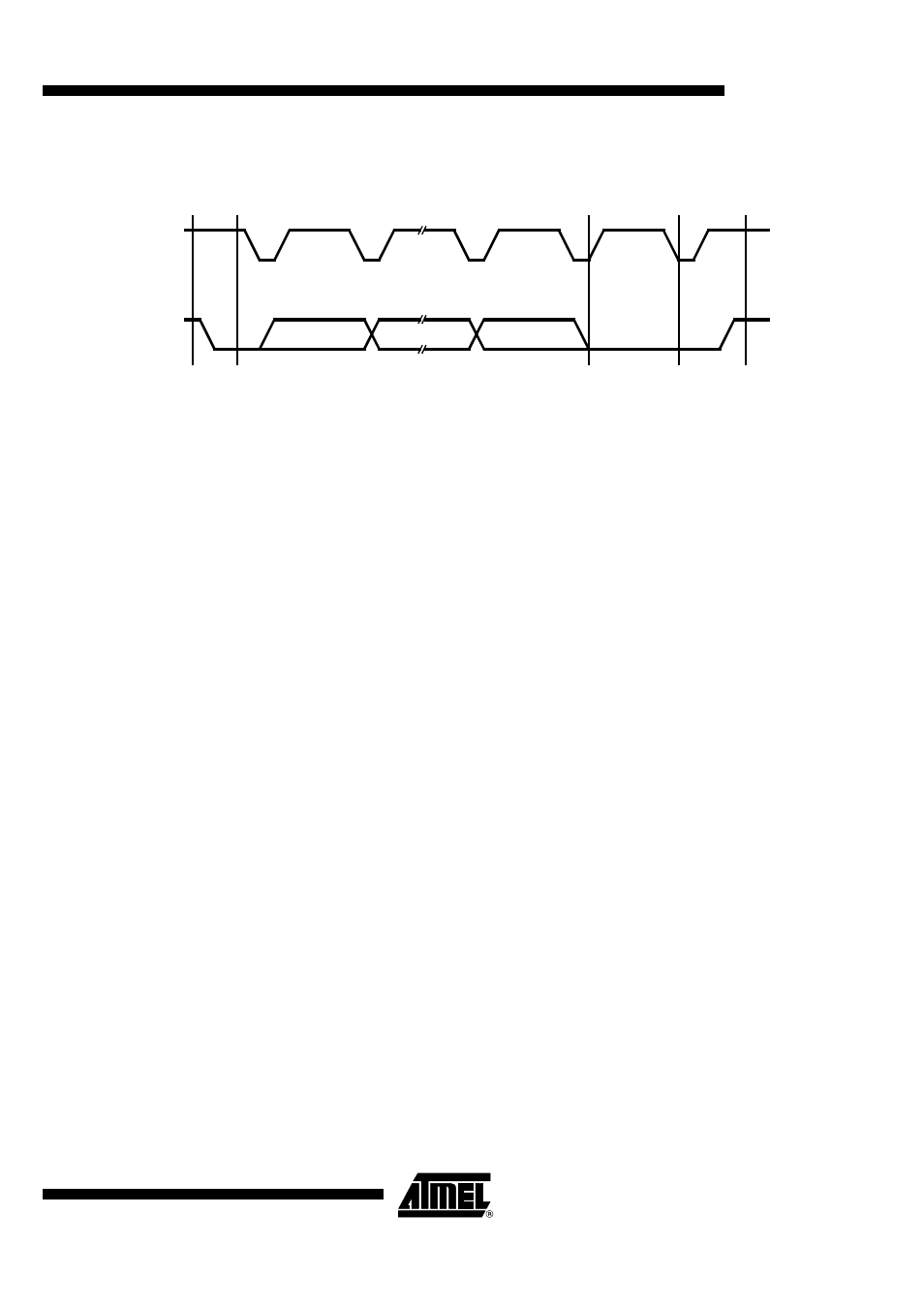

Figure 72.

MCL Bus Protocol 2

SSI Interrupt

The SSI interrupt INT3 can be generated either by an SSI buffer register status (i.e.,

transmit buffer empty or receive buffer full), the end of SSI data telegram or on the fall-

ing edge of the SC/SD pins on Port 4 (see P4CR). SSI interrupt selection is performed

by the Interrupt FunctioN control bit (IFN). The SSI interrupt is usually used to synchro-

nize the software control of the SSI and inform the controller of the present SSI status.

The Port 4 interrupts can be used together with the SSI or, if the SSI itself is not

required, as additional external interrupt sources. In either case this interrupt is capable

of waking the controller out of sleep mode.

To enable and select the SSI relevant interrupts use the SSI interrupt mask (SIM) and

the Interrupt Function (IFN) while the Port 4 interrupts are enabled by setting appropri-

ate control bits in P4CR register.

Modulation and Demodulation

If the shift register is used together with Timer 2 or Timer 3 for modulation or demodula-

tion purposes, the 8-bit synchronous mode must be used. In this case, the unused Port

4 pins can be used as conventional bi-directional ports.

The modulation and demodulation stages, if enabled, operate as soon as the SSI is acti-

vated (SIR = 0) and cease when deactivated (SIR = 1).

Due to the byte-orientated data control, the SSI (when running normally) generates

serial bit streams which are submultiples of 8 bits. An SSI output masking (OMSK) func-

tion permits; however, the generation of bit streams of any length. The OMSK signal is

derived indirectly from the 4-bit prescaler of the Timer 2 and masks out a programmable

number of unrequired trailing data bits during the shifting out of the final data word in the

bit stream. The number of non-masked data bits is defined by the value pre-pro-

grammed in the prescaler compare register. To use output masking, the modulator stop

mode bit (MSM) must be set to "0" before programming the final data word into the SSI

transmit buffer. This in turn, enables shift clocks to the prescaler when this final word is

shifted out. On reaching the compare value, the prescaler triggers the OMSK signal and

all following data bits are blanked.

Internal 2-wire Multi-chip Link

Two additional on-chip pads (MCL_SC and MCL_SD) for the SC and the SD line can be

used as chip-to-chip link for multi-chip applications. These pads can be activated by set-

ting the MCL-bit in the SISC-register.

SC

SD

Start

1

n

8

9

1st Bit

8th Bit

ACK

Stop