Clock management, Clock management register (cm), Atar862-8 – Rainbow Electronics ATAR862-8 User Manual

Page 28

28

ATAR862-8

4589B–4BMCU–02/03

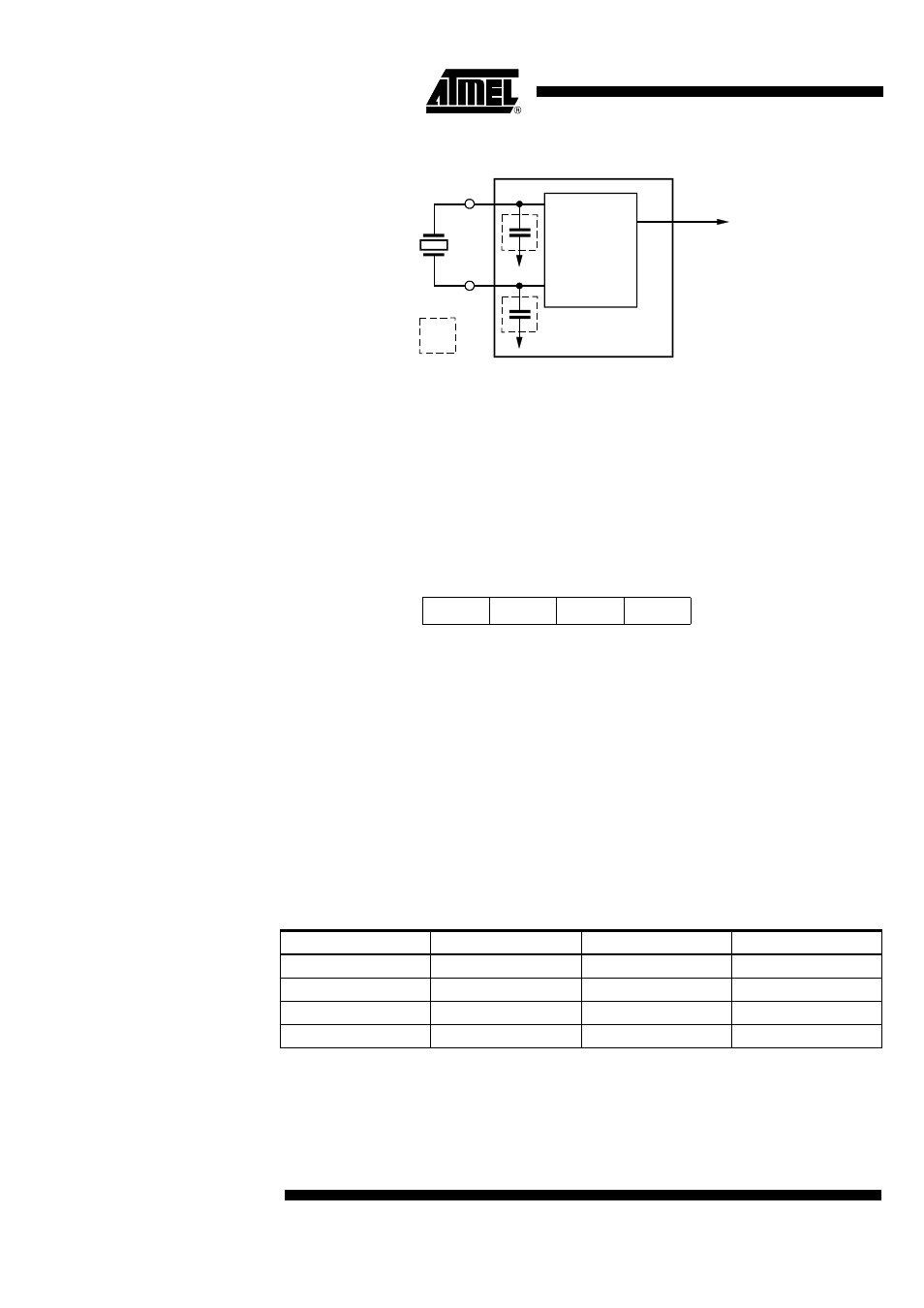

Figure 27.

32-kHz Crystal Oscillator

Clock Management

The clock management register controls the system clock divider and synchronization

stage. Writing to this register triggers the synchronization cycle.

Clock Management Register

(CM)

Auxiliary register address: "3"hex

32-kHz

oscillator

32Out

32Out

OSC1

OSC2

*

Oscin

C1

*

C2

Oscout

XTAL

32 kHz

*

mask option

Bit 3

Bit 2

Bit 1

Bit 0

CM:

NSTOP

CCS

CSS1

CSS0

Reset value: 1111b

NSTOP

N

ot

STOP

peripheral clock

NSTOP = 0, stops the peripheral clock while the core is in SLEEP mode

NSTOP = 1, enables the peripheral clock while the core is in SLEEP mode

CCS

C

ore

C

lock

S

elect

CCS = 1, the internal RC-oscillator 1 generates SYSCL

CCS = 0, the 4-MHz crystal oscillator, the 32-kHz crystal oscillator, an external

clock source or the internal RC-oscillator 2 with the external resistor at OSC1

generates SYSCL dependent on the setting of OS0 and OS1 in the system

configuration register

CSS1

C

ore

S

peed

S

elect

1

CSS0

C

ore

S

peed

S

elect

0

CSS1

CSS0

Divider

Note

0

0

16

–

1

1

8

Reset value

1

0

4

–

0

1

2

–