Watchdog reset, External clock supervisor, Voltage monitor – Rainbow Electronics ATAR862-8 User Manual

Page 22: Atar862-8

22

ATAR862-8

4589B–4BMCU–02/03

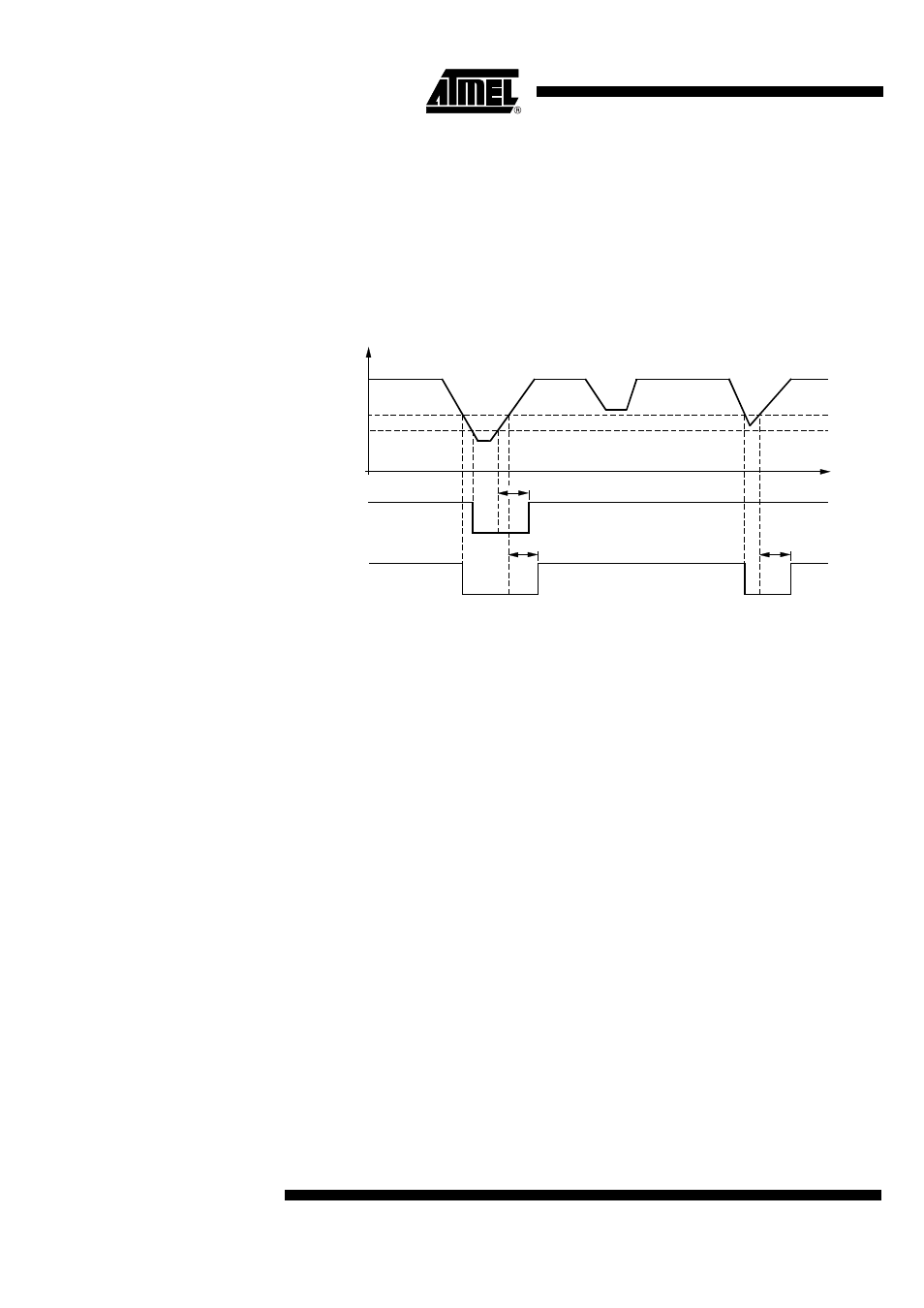

A power-on reset pulse is generated by a V

DD

rise across the default BOT voltage level

(1.7 V). A brown-out reset pulse is generated when V

DD

falls below the brown-out volt-

age threshold. Two values for the brown-out voltage threshold are programmable via

the BOT-bit in the SC-register. When the controller runs in the upper supply voltage

range with a high system clock frequency, the high threshold must be used. When it

runs with a lower system clock frequency, the low threshold and a wider supply voltage

range may be chosen. For further details, see the electrical specification and the SC-

register description for BOT programming.

Figure 17.

Brown-out Detection

Watchdog Reset

The watchdog’s function can be enabled at the WDC-register and triggers a reset with

every watchdog counter overflow. To suppress the watchdog reset, the watchdog

counter must be regularly reset by reading the watchdog register address (CWD). The

CPU reacts in exactly the same manner as a reset stimulus from any of the above

sources.

External Clock Supervisor

The external input clock supervisor function can be enabled if the external input clock is

selected within the CM- and SC-registers of the clock module. The CPU reacts in

exactly the same manner as a reset stimulus from any of the above sources.

Voltage Monitor

The voltage monitor consists of a comparator with internal voltage reference. It is used

to supervise the supply voltage or an external voltage at the VMI-pin. The comparator

for the supply voltage has three internal programmable thresholds one lower threshold

(2.2 V), one middle threshold (2.6 V) and one higher threshold (3.0 V). For external volt-

ages at the VMI-pin, the comparator threshold is set to V

BG

= 1.3 V. The VMS-bit

indicates if the supervised voltage is below (VMS = 0) or above (VMS = 1) this thresh-

old. An interrupt can be generated when the VMS-bit is set or reset to detect a rising or

falling slope. A voltage monitor interrupt (INT7) is enabled when the interrupt mask bit

(VIM) is reset in the VMC-register.

V

DD

CPU

Reset

t

BOT = '1'

2.0 V

1.7 V

CPU

Reset

BOT = '0'

td

td

t

d

= 1.5 ms (typically)

td

BOT = 1, low brown-out voltage threshold 1.7 V (is reset value).

BOT = 0, high brown-out voltage threshold 2.0 V.